5、小外形封裝(SOP)

SOP(Small Out-Line Package)是表面貼裝型封裝之一,也稱之為SOL或DFP,引腳從封裝兩側(cè)引出呈海鷗翼狀(L字形)。材料有塑料和陶瓷兩種。

SOP封裝標(biāo)準(zhǔn)有SOP-8、SOP-16、SOP-20、SOP-28等,SOP后面的數(shù)字表示引腳數(shù)。MOSFET的SOP封裝多數(shù)采用SOP-8規(guī)格,業(yè)界往往把“P”省略,簡(jiǎn)寫為SO(Small Out-Line)。

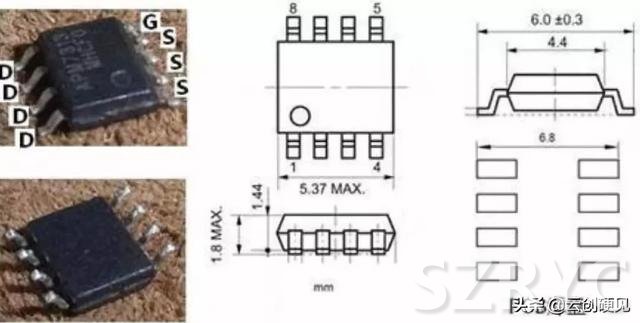

SOP-8封裝尺寸

SO-8為PHILIP公司率先開發(fā),采用塑料封裝,沒(méi)有散熱底板,散熱不良,一般用于小功率MOSFET。

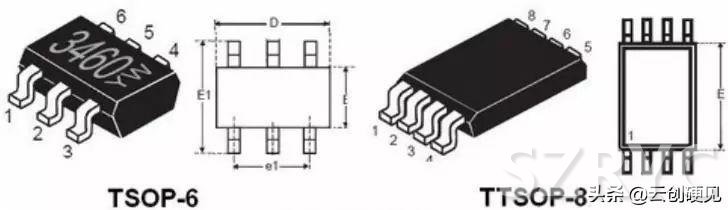

后逐漸派生出TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)等標(biāo)準(zhǔn)規(guī)格;其中TSOP和TSSOP常用于MOSFET封裝。

常用于MOS管的SOP派生規(guī)格

6、方形扁平式封裝(QFP)

QFP(Plastic Quad Flat Package)封裝的芯片引腳之間距離很小,管腳很細(xì),一般在大規(guī)模或超大型集成電路中采用,其引腳數(shù)一般在100個(gè)以上。

用這種形式封裝的芯片必須采用SMT表面安裝技術(shù)將芯片與主板焊接起來(lái)。該封裝方式具有四大特點(diǎn):

①適用于SMD表面安裝技術(shù)在PCB電路板上安裝布線;

②適合高頻使用;

③操作方便,可靠性高;

④芯片面積與封裝面積之間的比值較小。

與PGA封裝方式一樣,該封裝方式將芯片包裹在塑封體內(nèi),無(wú)法將芯片工作時(shí)產(chǎn)生的熱量及時(shí)導(dǎo)出,制約了MOSFET性能的提升;而且塑封本身增加了器件尺寸,不符合半導(dǎo)體向輕、薄、短、小方向發(fā)展的要求;另外,此類封裝方式是基于單顆芯片進(jìn)行,存在生產(chǎn)效率低、封裝成本高的問(wèn)題。

因此,QFP更適于微處理器/門陳列等數(shù)字邏輯LSI電路采用,也適于VTR信號(hào)處理、音響信號(hào)處理等模擬LSI電路產(chǎn)品封裝。

7、四邊無(wú)引線扁平封裝(QFN)

QFN(Quad Flat Non-leaded package)封裝四邊配置有電極接點(diǎn),由于無(wú)引線,貼裝表現(xiàn)出面積比QFP小、高度比QFP低的特點(diǎn);其中陶瓷QFN也稱為L(zhǎng)CC(Leadless Chip Carriers),采用玻璃環(huán)氧樹脂印刷基板基材的低成本塑料QFN則稱為塑料LCC、PCLC、P-LCC等。

是一種焊盤尺寸小、體積小、以塑料作為密封材料的新興表面貼裝芯片封裝技術(shù)。

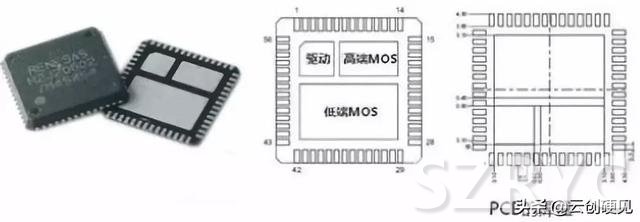

QFN主要用于集成電路封裝,MOSFET不會(huì)采用。不過(guò)因Intel提出整合驅(qū)動(dòng)與MOSFET方案,而推出了采用QFN-56封裝(“56”指芯片背面有56個(gè)連接Pin)的DrMOS。

需要說(shuō)明的是,QFN封裝與超薄小外形封裝(TSSOP)具有相同的外引線配置,而其尺寸卻比TSSOP的小62%。根據(jù)QFN建模數(shù)據(jù),其熱性能比TSSOP封裝提高了55%,電性能(電感和電容)比TSSOP封裝分別提高了60%和30%。最大的缺點(diǎn)則是返修難度高。

采用QFN-56封裝的DrMOS

隨著技術(shù)的革新與進(jìn)步,把驅(qū)動(dòng)器和MOSFET整合在一起,構(gòu)建多芯片模塊已經(jīng)成為了現(xiàn)實(shí),這種整合方式同時(shí)可以節(jié)省相當(dāng)可觀的空間從而提升功耗密度,通過(guò)對(duì)驅(qū)動(dòng)器和MOS管的優(yōu)化提高電能效率和優(yōu)質(zhì)DC電流,這就是整合驅(qū)動(dòng)IC的DrMOS。

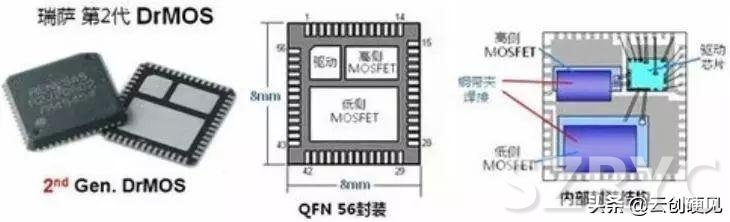

瑞薩第2代DrMOS

經(jīng)過(guò)QFN-56無(wú)腳封裝,讓DrMOS熱阻抗很低;借助內(nèi)部引線鍵合以及銅夾帶設(shè)計(jì),可最大程度減少外部PCB布線,從而降低電感和電阻。

另外,采用的深溝道硅(trench silicon)MOSFET工藝,還能顯著降低傳導(dǎo)、開關(guān)和柵極電荷損耗;并能兼容多種控制器,可實(shí)現(xiàn)不同的工作模式,支持主動(dòng)相變換模式APS(Auto Phase Switching)。

除了QFN封裝外,雙邊扁平無(wú)引腳封裝(DFN)也是一種新的電子封裝工藝,在安森美的各種元器件中得到了廣泛采用,與QFN相比,DFN少了兩邊的引出電極。

8、塑封有引線芯片載體(PLCC)

PLCC(Plastic Quad Flat Package)外形呈正方形,尺寸比DIP封裝小得多,有32個(gè)引腳,四周都有管腳,引腳從封裝的四個(gè)側(cè)面引出,呈丁字形,是塑料制品。

其引腳中心距1.27mm,引腳數(shù)從18到84不等,J形引腳不易變形,比QFP容易操作,但焊接后的外觀檢查較為困難。PLCC封裝適合用SMT表面安裝技術(shù)在PCB上安裝布線,具有外形尺寸小、可靠性高的優(yōu)點(diǎn)。

PLCC封裝是比較常見(jiàn),用于邏輯LSI、DLD(或程邏輯器件)等電路,主板BIOS常采用的這種封裝形式,不過(guò)目前在MOS管中較少見(jiàn)。

PLCC封裝樣式

主流企業(yè)的封裝與改進(jìn)

由于CPU的低電壓、大電流的發(fā)展趨勢(shì),對(duì)MOSFET提出輸出電流大,導(dǎo)通電阻低,發(fā)熱量低散熱快,體積小的要求。MOSFET廠商除了改進(jìn)芯片生產(chǎn)技術(shù)和工藝外,也不斷改進(jìn)封裝技術(shù),在與標(biāo)準(zhǔn)外形規(guī)格兼容的基礎(chǔ)上,提出新的封裝外形,并為自己研發(fā)的新封裝注冊(cè)商標(biāo)名稱。

1、瑞薩(RENESAS)WPAK、LFPAK和LFPAK-I封裝

WPAK是瑞薩開發(fā)的一種高熱輻射封裝,通過(guò)仿D-PAK封裝那樣把芯片散熱板焊接在主板上,通過(guò)主板散熱,使小形封裝的WPAK也可以達(dá)到D-PAK的輸出電流。WPAK-D2封裝了高/低2顆MOSFET,減小布線電感。

瑞薩WPAK封裝尺寸

LFPAK和LFPAK-I是瑞薩開發(fā)的另外2種與SO-8兼容的小形封裝。LFPAK類似D-PAK,但比D-PAK體積小。LFPAK-i是將散熱板向上,通過(guò)散熱片散熱。

瑞薩LFPAK和LFPAK-I封裝

2、威世(Vishay)Power-PAK和Polar-PAK封裝

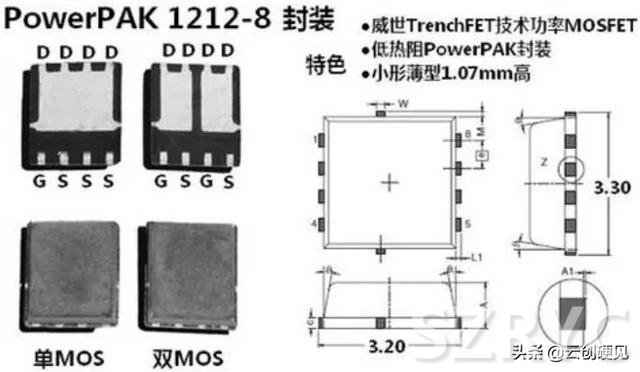

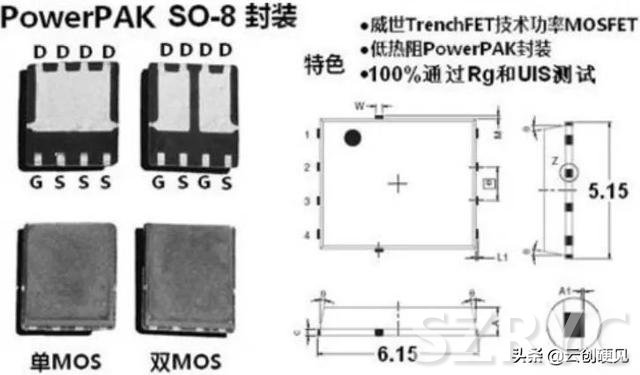

Power-PAK是威世公司注冊(cè)的MOSFET封裝名稱。Power-PAK包括有Power-PAK1212-8、Power-PAK SO-8兩種規(guī)格。

威世Power-PAK1212-8封裝

威世Power-PAK SO-8封裝

Polar PAK是雙面散熱的小形封裝,也是威世核心封裝技術(shù)之一。Polar PAK與普通的so-8封裝相同,其在封裝的上、下兩面均設(shè)計(jì)了散熱點(diǎn),封裝內(nèi)部不易蓄熱,能夠?qū)⒐ぷ麟娏鞯碾娏髅芏忍岣咧罶O-8的2倍。目前威世已向意法半導(dǎo)體公司提供Polar PAK技術(shù)授權(quán)。

威世Polar PAK封裝

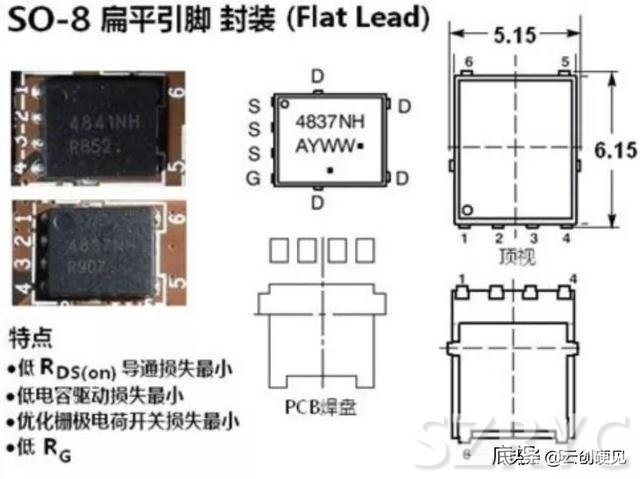

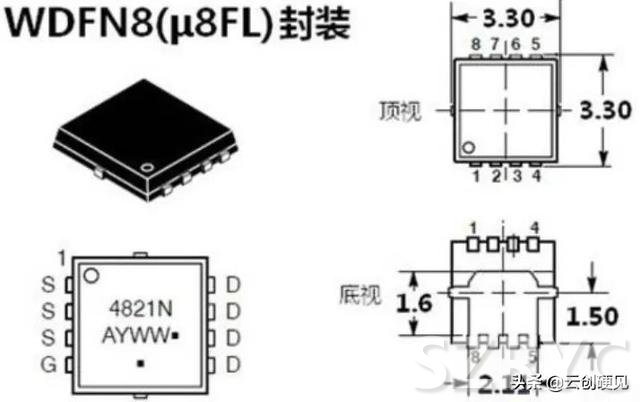

3、安森美(Onsemi)SO-8和WDFN8扁平引腳(Flat Lead)封裝

安美森半導(dǎo)體開發(fā)了2種扁平引腳的MOSFET,其中SO-8兼容的扁平引腳被很多板卡采用。安森美新近推出的NVMx和NVTx功率MOSFET就采用了緊湊型DFN5(SO-8FL)和WDFN8封裝,可最大限度地降低導(dǎo)通損耗,另外還具有低QG和電容,可將驅(qū)動(dòng)器損耗降到最低的特性。

安森美SO-8扁平引腳封裝

安森美WDFN8封裝

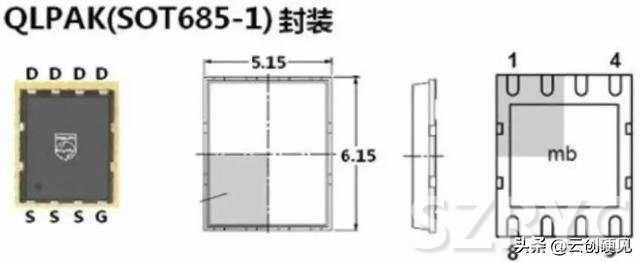

4、恩智浦(NXP)LFPAK和QLPAK封裝

恩智浦(原Philps)對(duì)SO-8封裝技術(shù)改進(jìn)為L(zhǎng)FPAK和QLPAK。其中LFPAK被認(rèn)為是世界上高度可靠的功率SO-8封裝;而QLPAK具有體積小、散熱效率更高的特點(diǎn),與普通SO-8相比,QLPAK占用PCB板的面積為6*5mm,同時(shí)熱阻為1.5k/W。

恩智浦LFPAK封裝

恩智浦QLPAK封裝