富昌電子(Future Electronics)一直致力于以專業的技術服務,為客戶打造個性化的解決方案,進而縮短產品的設計周期、加快行業發展的步伐。在第三代半導體的實際應用領域,富昌電子結合自身的技術、項目經驗積累,著筆SiC相關設計的系列文章,希望能給到大家一定的參考,并期待與您進一步的交流。

本文作為系列文章的第五篇,主要針對SiC?MOSFET相關應用中的EMI改善方案做一些探討。

對設計人員而言,成功應用 SiC MOSFET 的關鍵在于深入了解 SiC MOSFET 獨有的工作特征及其對設計的影響。SiC MOSFET的快速開關速度,高額定電壓和低RDS(on)使其對于不斷尋求在提高效率和功率密度的同時,保持系統簡單性的電源設計人員具有很高的吸引力。但是,由于高壓及超快的開關速度帶來的超高di/dt,dv/dt,會通過系統的雜散電感,電容形成干擾,比如SiC MOSFET過高的開關速度會引起Vds振鈴尖峰,因而產生EMI。

寄生電感是SiC MOSFET Vds尖峰和振鈴的主要原因。SiC MOSFET的快速開關速度會導致較高Vds尖峰和較長的振鈴時間。這種尖峰會降低設備的設計裕量,并且較長的振鈴時間會引入EMI。在大電流情況下,該現象更加明顯。

判斷EMI是否來源于di/dt與dv/dt,以及采用合適的、有針對性的方案就顯得尤為重要,常見的EMI解決方案技術如下:

1, 通過使用高柵極電阻(Rgon, Rgoff)來實現降低通過器件的電流變化率(dI/dt). 高的Rg會顯著增加開關損耗, 需要在效率和EMI平衡。

2,通過使用門極漏極電容Cgd來降低器件Vds的電壓變化率(dv/dt), 高的Cgd同樣會增加開關損耗, 需要在效率和EMI平衡。

3, 降低功率環路的雜散電感,最大限度縮短導線長度,降低?PCB布局的電感(如將柵極驅動器放在盡可能靠近 MOSFET 的位置,并使用疊接式導線幾何形狀而不是并排(共平面)幾何形狀),也是改善EMI的有效方法,需要在最小間距和間隙安全規定平衡。

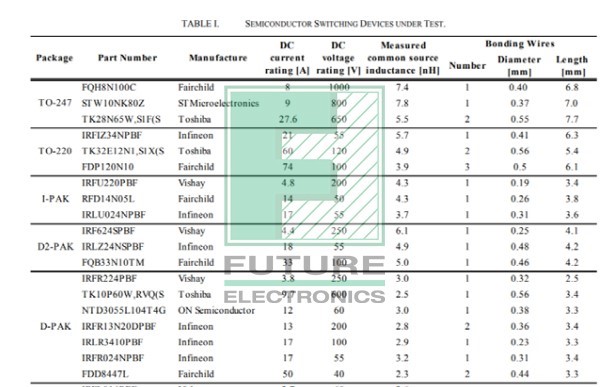

4,使用新的封裝如貼片低引線電感(如圖一),封裝電感是決定切換時間的關鍵參數,而切換時間與開關速度和EMI等密切相關,需要在的封裝和熱性能平衡。

5,新的數控技術(如頻率抖動, 軟開關技術等) 對低和高頻段的EMI有好處 。

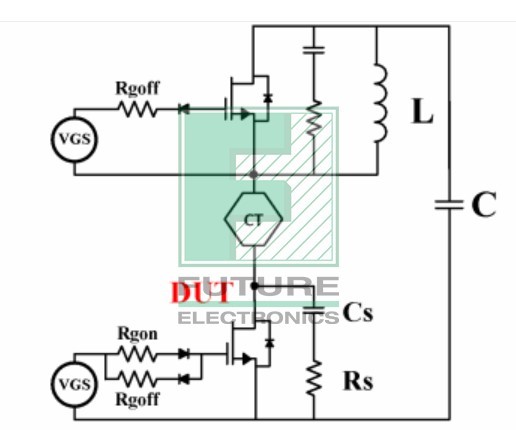

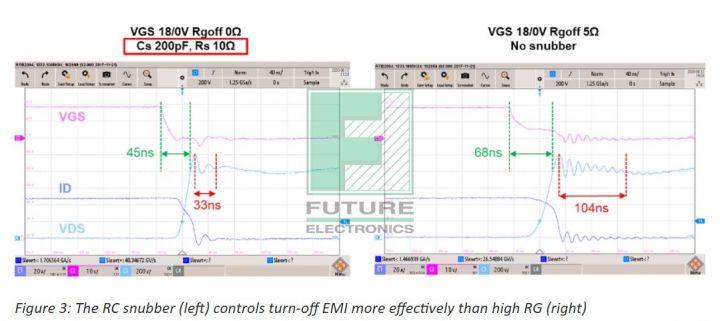

6,使用緩沖器(如RCD) 對Vds振蕩尖峰做吸收(如圖二),也能明顯改善Vds抖動和EMI(如圖三所示測試結果),但是需要在效率和EMI平衡。相比于調節Rg,該方案相對高效。

?

結論: 以上是富昌電子與客戶工程師交流總結的EMI方案,供參考。 由于EMI的產生原因和機理不同,方案也不一樣,有時需要多種方案綜合評估。如需進一步探討,請聯系富昌電子技術方案中心。