超越摩爾,三星的異構集成之路

在近期舉辦的2021年SamsungFoundry論壇上,三星透露了2/3nm制程工藝的新進展,并公開發布了全新的17nm工藝。三星市場戰略副總裁MoonSoo Kang也面向產業合作伙伴,公布了三星在異構集成上的計劃,如何為摩爾定律再度添加一個“維度”。

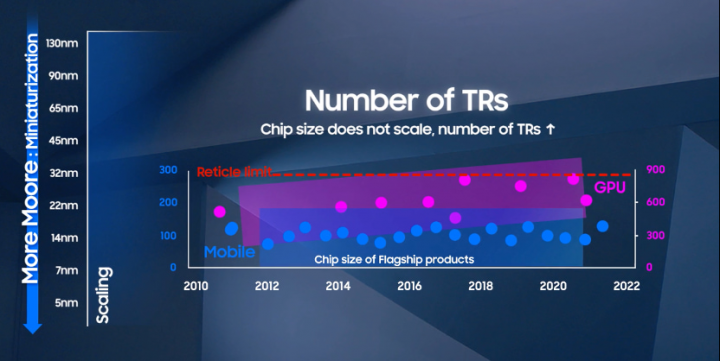

旗艦GPU與移動芯片的面積變化對比 / 三星

幾十年間,半導體產業一直在不懈地推動摩爾定律,以更先進的制程做到更多的晶體管數目,這就是我們常說的“延續摩爾”方案,也是當前計算與電路領域持續創新最大的推動力。

盡管摩爾定律的延續,芯片面積仍在擴大,比如一直在追求算力的GPU,已經快要逼近光罩尺寸的限度了。再加上晶體管數目的增加,使得芯片設計成本和生產成本無休止地增加。在不少人看來,單靠“延續摩爾”不再是一個技術與成本上可持續的方案。

與此同時,更多的功能與特性集成在單個芯片上,卻又沒有單個制程可以滿足所有不同功能的需求,比如模擬、射頻、高壓等,即便可以滿足也無法達到優秀的性能與成本平衡。“延續摩爾”的方案在這類挑戰面前束手無策,因此才出現了異構集成這種“擴展摩爾”的方案。通過兩種方案的互補,共同做到“超越摩爾”。

Chiplet:降低成本提高良率的救星

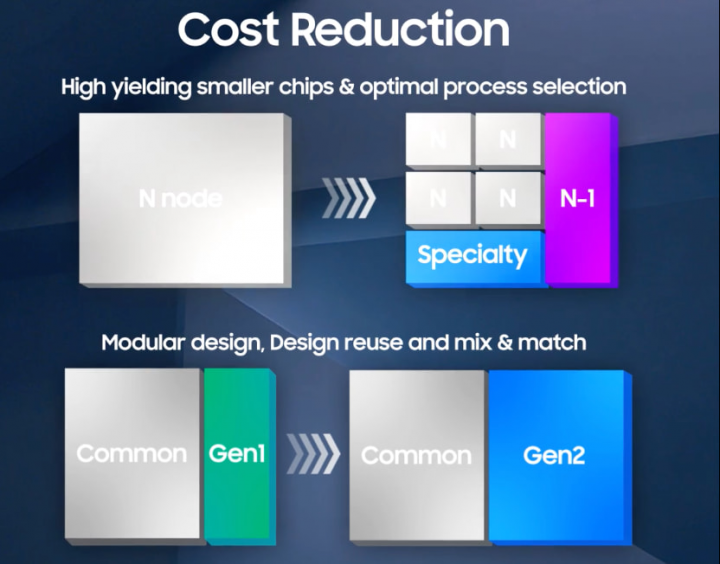

隨著單個芯片加入更多特性,即便摩爾定律延續下去,其芯片面積仍在增加,為所有不同功能的設計區塊使用同一個制程節點成了抵消的選擇,好在如今有了Chiplet這一救星的出現。將一大塊裸片分成較小的chiplet,并為每個chiplet使用最優的制程,可以顯著提高整個芯片的良率,同時減少生產成本。例如某些特定的接口IP并不會因為采用先進制程而獲得面積或性能上的優化,對這些IP使用成熟制程和專用定制制程,可以做到更低的成本以及更優的性能。

Chiplet方案 / 三星

另一個可行方案就是模組化的設計與制造,也就是重復使用相同的組件chiplet。不少IP模組都可以作為chiplet重復使用,只有芯片的其他部分需要重新設計和生產,此舉顯著減少了設計、開發與生產的成本,芯片廠商可以借此更快實現產品迭代。

X-Cube:垂直3D集成

異構集成不只是為了成本和良率考慮,也能進一步提升芯片性能。傳統的2D設計中,信號路徑有幾毫米長。而在3D集成下,芯片的堆疊可以將信號路徑減少至幾微米,大大改進了芯片延遲。除此之外,3D集成中更出色的內聯間距可以實現更高的帶寬,進一步提高芯片性能。

早在2014年,三星就首次實現了將寬IO內存與移動應用處理器的3D堆疊,也就是三星的Widcon技術。隨后,3D芯片堆疊技術繼續發展,誕生了一系列HBM內存產品。HBM就是由DRAM與邏輯堆疊,并由微凸塊和TSV相連而成的。也正是因為3D堆疊技術,三星得以開發出了3層的CMOS圖像傳感器,由圖像傳感器、邏輯與DRAM三種不同的裸片堆疊在一起而成。

2020年,三星推出了X-Cube技術,這項技術使得兩個邏輯單元裸片可以垂直堆疊在一起,形成一個單獨的3D芯片,由微凸塊與TSV連接。X-Cube分為兩種形式,兩個裸片由微凸塊連接或是直接銅鍵合。

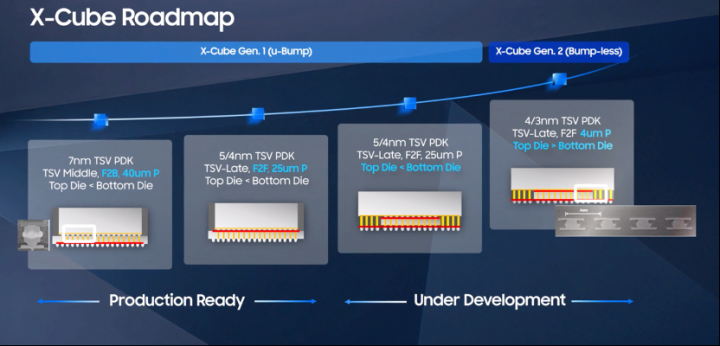

X-Cube路線圖 / 三星

第一代X-Cube技術(u-Bump)主要依靠微凸塊連接,三星已經發布了針對7nm邏輯制程的TSV PDK,采用F2B結構,凸塊間距為40um。面向4/5nm的TSV PDK也已經發布,改用F2F的結構,凸塊間距降低至25um。尚在開發中的第二代X-Cube技術(Bump-less)則采用了直接銅鍵合技術,間距降低至4um。

值得一提的是,英特爾的Foveros3D堆疊技術路線與三星X-Cube大致相同。第一代Foveros的凸塊間距在36um至50um之間,而下一代FoverosOmni技術同樣可以做到25um的凸塊間距。尚在開發的Foveros Direct也采用了直接銅鍵合的方式,宣稱凸塊間距降低至10um以下。

過去的X-Cube架構中,底部裸片的面積要大于頂部裸片,然而為了更好了滿足客戶對芯片分區和散熱等不同要求,三星也將在后續提供頂部裸片大于底部裸片的結構。目前三星已經完成了3D堆疊SRAM的驗證,在7nm的制程下,可以做到48.6GB/s的帶寬,以及7.2ns的讀取延遲與2.6ns的寫入延遲。

除此之外,三星還提供了一項差異化技術,ISC(集成堆疊電容)。這一電容應用了已經在三星DRAM產品中獲得驗證的硅電容結構、材料和工藝,具有1100nF/mm2的電容密度,可以有效提高電源完整性。三星的ISC還提供了多種不同的配置,比如分立型、硅中介層型和多晶圓堆疊型,以滿足客戶不同的結構需求,ISC預計將在2022年進入量產階段。

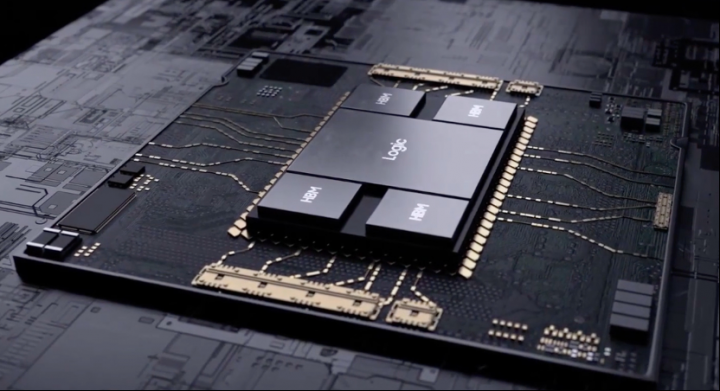

I-Cube:橫向2.5D組合

另一方面,為了從橫向組合芯片,三星開發了所謂的2.5D技術I-Cube,將邏輯單元與多個HBM集成在同一硅中介層上。目前三星已經成功實現了一個邏輯裸片+兩個HBM的I-Cube2量產,成品之一就是百度的昆侖AI芯片。百度的昆侖AI芯片不僅使用了三星的14nm制程,也運用了三星的I-CUBE 2技術。

I-Cube使用了預篩選的技術,在封裝的中間階段進行運算測試,從而提高良率。該技術還采用了無封膠的結構,做到更好的散熱性能,據三星強調,與傳統的2.5D方案相比,I-Cube的散熱效率高上4.5%。此外,與其他代工廠商相比,三星的I-Cube技術還有一些優勢,比如與三星內存合作,率先用上最新的內存方案

I-Cube4示意圖 / 三星

目前三星已經在計劃集成4HBM3模組的I-Cube4量產工作,而6 HBM的I-Cube6也已經做好量產準備,前者預計2022年進入大批量產階段。三星更是準備了兩個邏輯裸片+8個HBM的I-Cube8方案,目前尚處于開發階段,預計2022年末將正式上線。

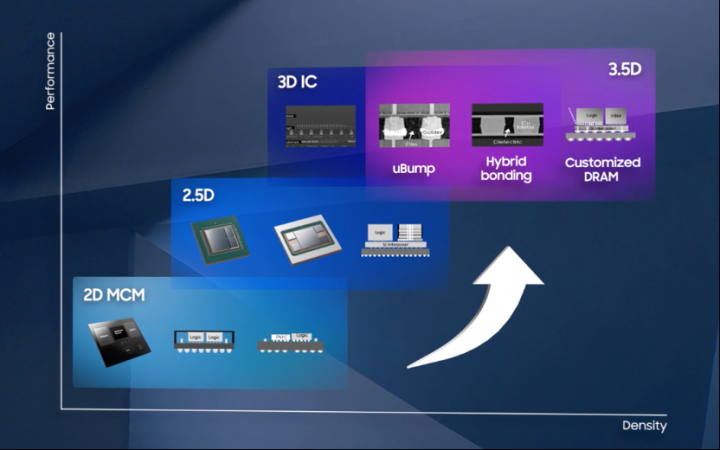

2D至3.5D的封裝方案 / 三星

除了2D、2.5D與3D的IC技術之外,三星還在開發全新的3.5D封裝技術,這種系統級封裝內還將加入堆疊的定制DRAM或SRAM裸片,實現更高的性能與密度。

小結

在開發2.5D/3D集成的多芯片或多Chiplet系統級芯片時,設計者往往還會遇到在傳統單芯片設計上罕見的技術障礙,比如多出來的接口IP或潛在的功耗增加。這時候,三星、臺積電和剛進入IDM 2.0的英特爾等代工廠商還會提供異構設計的方法和工具,幫助設計者克服這些挑戰。在異構集成的大勢之下,代工廠也將提供更多的服務模式,增加封裝、測試以及一站式的設計服務。