作者:ADI公司 Bhakti Waghmare和Diarmuid Carey

有限且不斷縮小的電路板空間、緊張的設計周期以及嚴格的電磁干擾(EMI)規范(例如CISPR 32和CISPR 25)這些限制因素,都導致獲得具有高效率和良好熱性能電源的難度很大。在整個設計周期中,電源設計通常基本處于設計過程的最后階段,設計人員需要努力將復雜的電源擠進更緊湊的空間,這使問題變得更加復雜,非常令人沮喪。為了按時完成設計,只能在性能方面做些讓步,把問題丟給測試和驗證環節去處理。簡單、高性能和解決方案尺寸三個考慮因素通常相互沖突:只能優先考慮一兩個,而放棄第三個,尤其當設計期限臨近時。犧牲一些性能變得司空見慣;其實不應該是這樣的。

本文首先概述了在復雜的電子系統中電源帶來的嚴重問題:即EMI,通常簡稱為噪聲。電源會產生EMI,必須加以解決,那么問題的根源是什么?通常有何緩解措施?本文介紹減少EMI的策略,提出了一種解決方案,能夠減少EMI、保持效率,并將電源放入有限的解決方案空間中。

電磁干擾是會干擾系統性能的電磁信號。這種干擾通過電磁感應、靜電耦合或傳導來影響電路。它對汽車、醫療以及測試與測量設備制造商來說,是一項關鍵設計挑戰。上面提到的許多限制和不斷提高的電源性能要求(功率密度增加、開關頻率更高以及電流更大)只會擴大EMI的影響,因此亟需解決方案來減少EMI。許多行業都要求必須滿足EMI標準,如果在設計初期不加以考慮,則會嚴重影響產品的上市時間。

EMI是電子系統中的干擾源與接收器(即電子系統中的一些元件)耦合時所產生的問題。EMI按其耦合介質可歸類為:傳導或輻射。

傳導EMI(低頻,450 kHz至30 MHz)

傳導EMI通過寄生阻抗以及電源和接地連接以傳導方式耦合到元件。噪聲通過傳導傳輸到另一個器件或電路。傳導EMI可以進一步分為共模噪聲和差模噪聲。

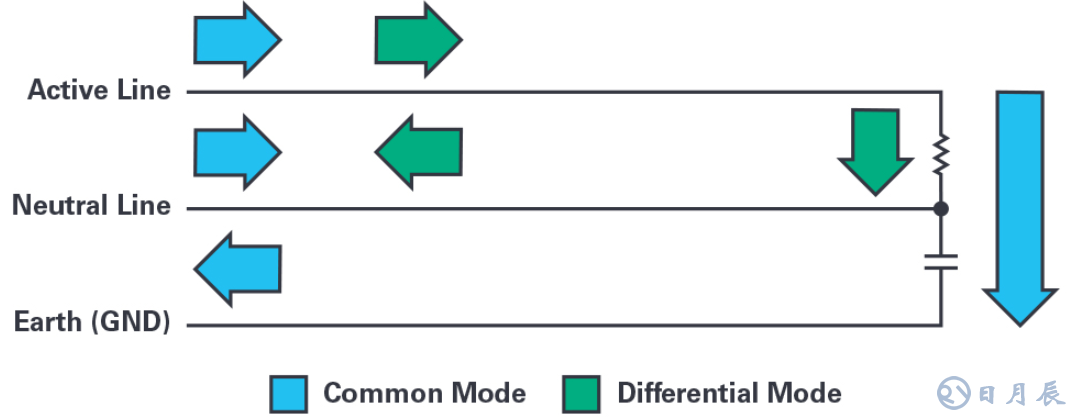

共模噪聲通過寄生電容和高dV/dt (C × dV/dt)進行傳導。它通過寄生電容沿著任意信號(正或負)到GND的路徑傳輸,如圖1所示。

DifferenTIal-mode noise is conducted via parasiTIc inductance (magneTIc coupling) and a high di/dt (L × di/dt)。

差模噪聲通過寄生電感(磁耦合)和高di/dt (L × di/dt)進行傳導。

圖1.差模和共模噪聲。

輻射EMI(高頻,30 MHz 至1 GHz)

輻射EMI是通過磁場能量以無線方式傳輸到待測器件的噪聲。在開關電源中,該噪聲是高di/dt與寄生電感耦合的結果。輻射噪聲會影響鄰近的器件。

解決電源中EMI相關問題的典型方法是什么?首先,確定EMI就是一個問題。這看似很顯而易見,但是確定其具體情況可能非常耗時,因為它需要使用EMI測試室(并非隨處都有),以便對電源產生的電磁能量進行量化,并確定該電磁能量是否符合系統的EMI標準要求。

假設經過測試,電源會帶來EMI問題,那么設計人員將面臨通過多種傳統的校正策略來減少EMI的過程,其中包括:

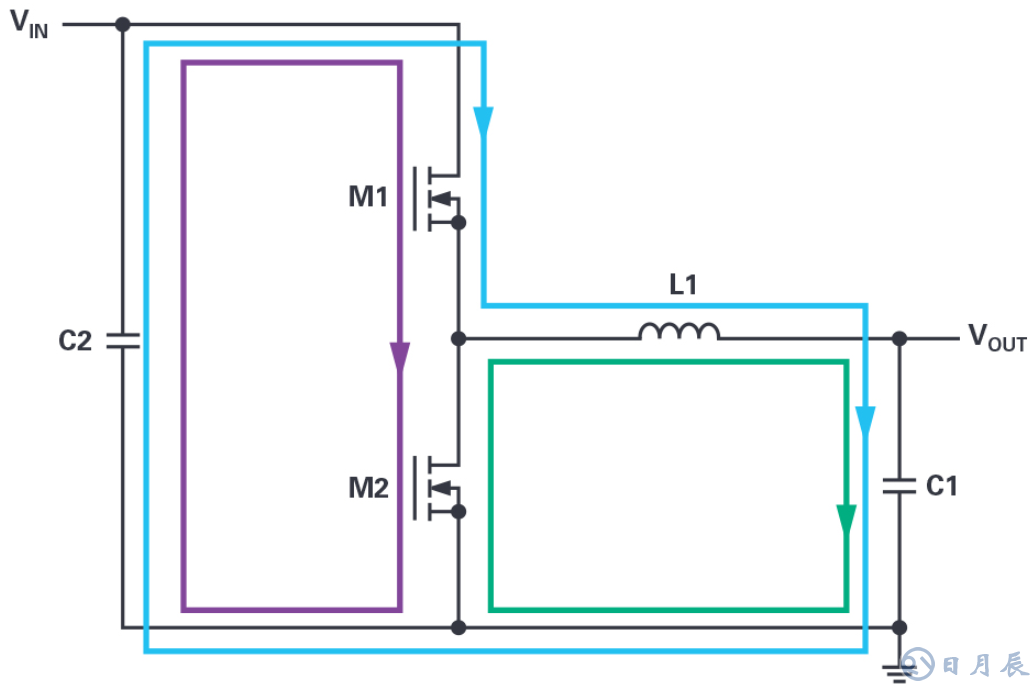

為了減少EMI,必須確定電源電路中的熱回路(高di/dt回路)并減少其影響。熱回路如圖2所示。在標準降壓轉換器的一個周期內,當M1關閉而M2打開時,交流電流沿著藍色回路流動。在M1打開而M2關閉的關閉周期中,電流沿著綠色回路流動。產生最高EMI的回路并非完全直觀可見,它既不是藍色回路也不是綠色回路,而是傳導全開關交流電流(從零切換到IPEAK,然后再切換回零)的紫色回路。該回路稱為熱回路,因為它的交流和EMI能量最大。

導致電磁噪聲和開關振鈴的是開關穩壓器熱回路中的高di/dt和寄生電感。要減少EMI并改進功能,需要盡量減少紫色回路的輻射效應。熱回路的電磁輻射騷擾隨其面積的增加而增加,因此,如果可能的話,將熱回路的PC面積減小到零,并使用零阻抗理想電容可以解決該問題。

圖2.降壓轉換器的熱回路。

雖然不可能完全消除熱回路區域,但是我們可以將熱回路分成極性相反的兩個回路。這可以有效地形成局部磁場,這些磁場在距IC任意位置都可以有效地相互抵消。這就是Silent Switcher穩壓器背后的概念。

圖3.Silent Switcher穩壓器中的磁場抵消。

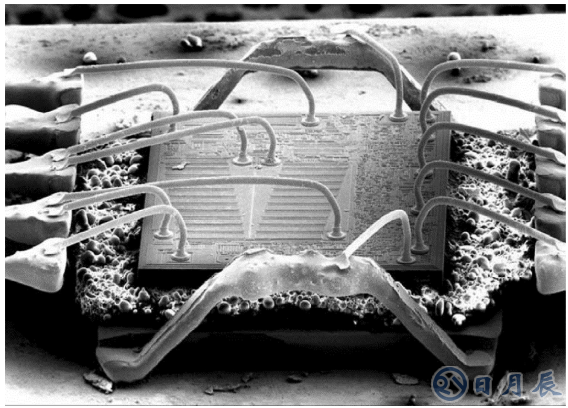

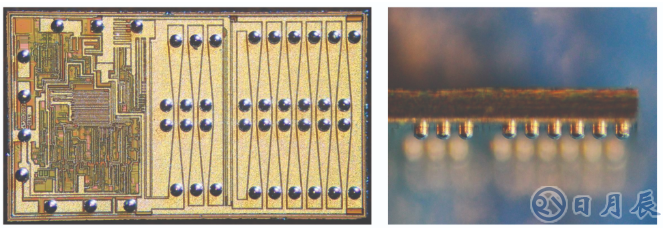

改善EMI的另一種方法是縮短熱回路中的導線。這可以通過放棄將芯片連接至封裝引腳的傳統鍵合線方法來實現。在封裝中倒裝硅芯片,并添加銅柱。通過縮短內部FET到封裝引腳和輸入電容的距離,可以進一步縮小熱回路的范圍。

圖4.LT8610鍵合線的拆解示意圖。

圖5.帶有銅柱的倒裝芯片。

Silent Switcher與Silent Switcher 2

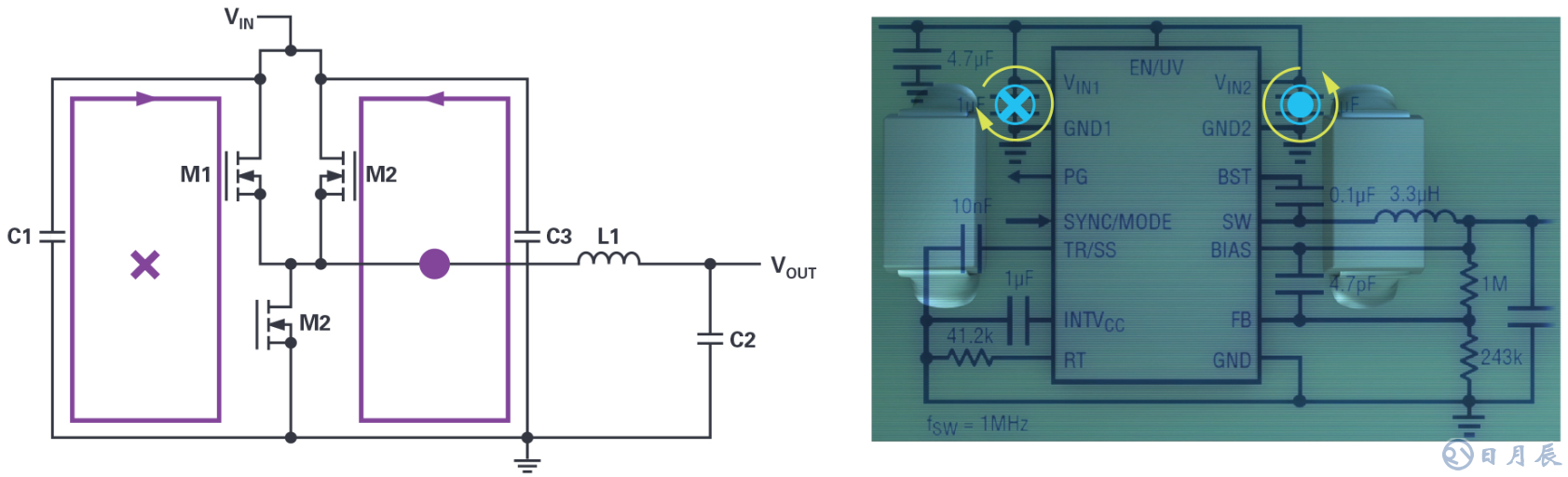

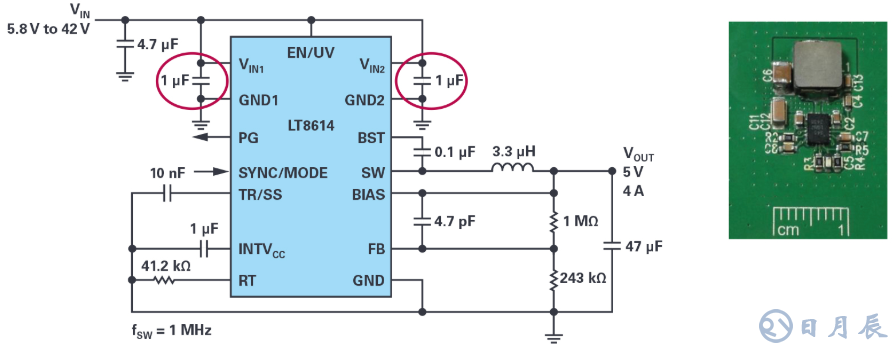

圖6.典型的Silent Switcher應用原理圖及其在PCB上的外觀。

圖6顯示了使用Silent Switcher穩壓器的一個典型應用,可通過兩個輸入電壓引腳上的對稱輸入電容來識別。布局在該方案中非常重要,因為Silent Switcher技術要求盡可能將這些輸入電容對稱布置,以便發揮場相互抵消的優勢。否則,將喪失Silent Switcher技術的優勢。當然,問題是如何確保在設計及整個生產過程中的正確布局。答案就是Silent Switcher 2穩壓器。

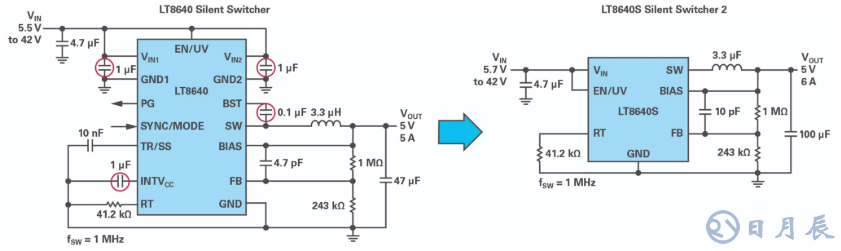

Silent Switcher 2

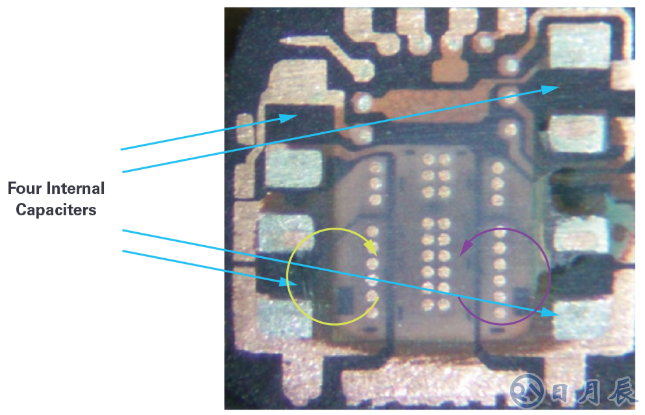

Silent Switcher 2穩壓器能夠進一步減少EMI。通過將電容(VIN電容、INTVCC和升壓電容)集成到LQFN封裝中,消除了EMI性能對PCB布局的敏感性,從而可以放置到盡可能靠近引腳的位置。所有熱回路和接地層都在內部,從而將EMI降至最低,并使解決方案的總占板面積更小。

圖7.Silent Switcher應用與Silent Switcher 2應用框圖。

圖8.去封的LT8640S Silent Switcher 2穩壓器。

Silent Switcher 2技術還可以改善熱性能。LQFN倒裝芯片封裝上的多個大尺寸接地裸露焊盤有助于封裝通過PCB散熱。消除高電阻鍵合線還可以提高轉換效率。在進行EMI性能測試時,LT8640S 能滿足CISPR 25 Class 5峰值限制要求,并且具有較大的裕量。

借助開發Silent Switcher產品組合所獲得的知識和經驗,并配合使用現有的廣泛µModule®產品組合,使我們提供的電源產品易于設計,同時滿足電源的某些重要指標要求,包括熱性能、可靠性、精度、效率和良好的EMI性能。

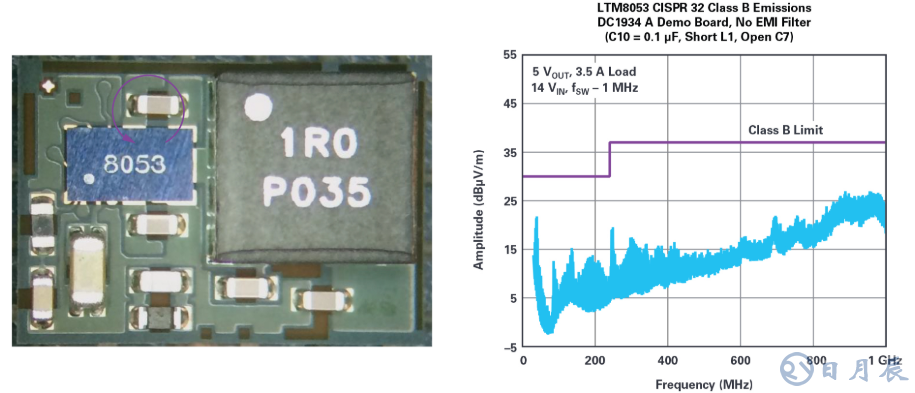

圖9所示的LTM8053集成了可實現磁場抵消的兩個輸入電容以及電源所需的其他一些無源組件。所有這些都通過一個 6.25 mm × 9 mm × 3.32 mm BGA封裝實現,讓客戶可以專心完成電路板的其他部分設計。

圖9.LTM8053 Silent Switcher裸露芯片及EMI結果。

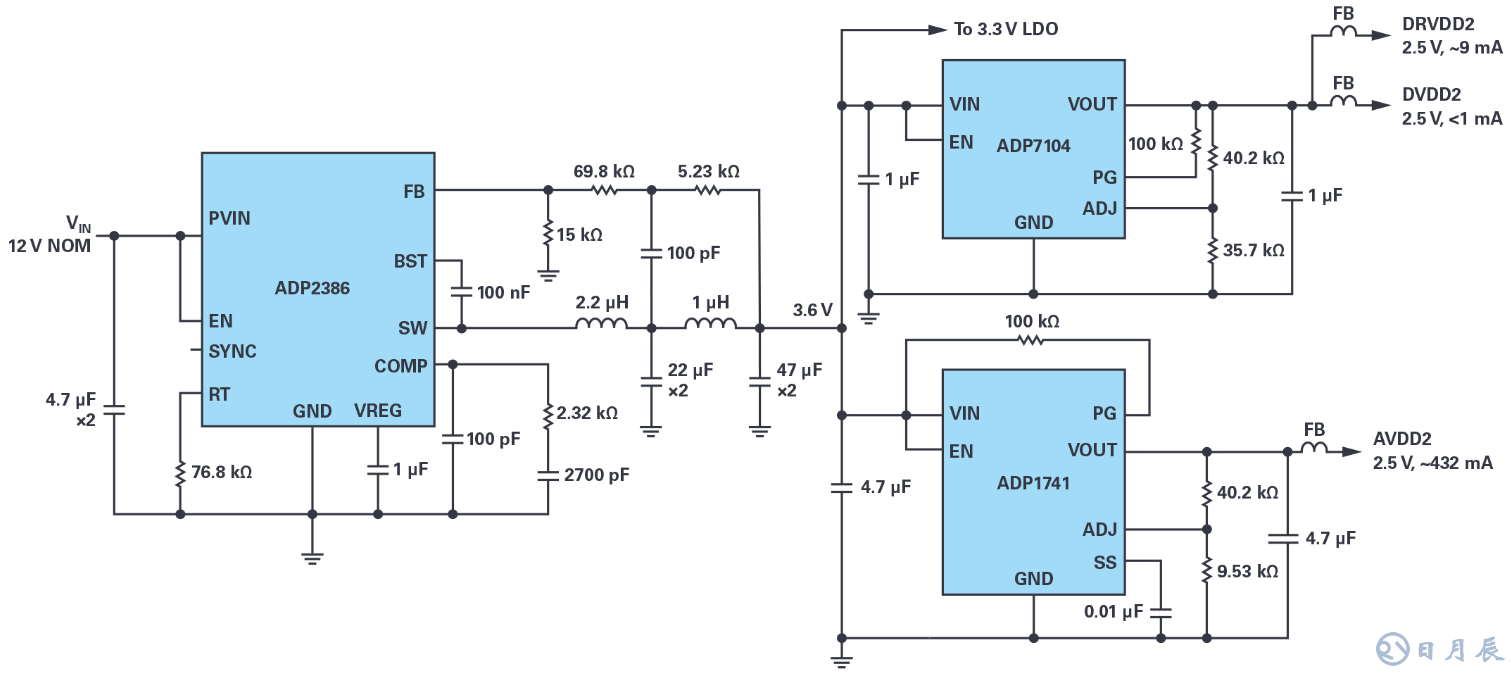

典型的高速ADC需要許多電壓軌,其中一些電壓軌噪聲必須非常低才能實現ADC數據表中的最高性能。為了在高效率、小尺寸板空間和低噪聲之間達成平衡,普遍接受的解決方案是將開關電源與LDO后置穩壓器結合使用,如圖10所示。開關穩壓器能夠以更高效率實現更高的降壓比,但噪聲相對也較大。低噪聲LDO后置穩壓器效率相對較低,但它可以抑制開關穩壓器產生的大部分傳導噪聲。盡可能減小LDO后置穩壓器的降壓比有助于提高效率。這種組合能產生干凈的電源,從而使ADC以最高性能運行。但問題在于多個穩壓器會使布局更復雜,并且LDO后置穩壓器在較高負載下可能會產生散熱問題。

圖10.為 AD9625 ADC供電的典型電源設計。

圖10所示的設計顯然需要進行一些權衡取舍。在這種情況下,低噪聲是優先考慮事項,因此效率和電路板空間必須做些讓步。但也許不必如此。最新一代的Silent Switcher µModule器件將低噪聲開關穩壓器設計與µModule封裝相結合,能夠同時實現易設計、高效率、小尺寸和低噪聲的目標。這些穩壓器不僅盡可能減少了電路板占用空間,而且實現了可擴展性,可使用一個µModule穩壓器為多個電壓軌供電,進一步節省了空間和時間。圖11顯示了使用LTM8065 Silent Switcher µModule穩壓器為ADC供電的電源樹替代方案。

圖11.使用Silent Switcher µModule穩壓器為AD9625供電,可節省空間的解決方案。

這些設計都已經過相互測試比較。ADI公司最近發表的一篇文章對使用圖10和圖11所示電源設計的ADC性能進行了測試和比較1。測試包括以下三種配置:

測得的SFDR和SNRFS結果表明,LTM8065可用于直接為ADC供電,并不會影響ADC的性能。

這個實施方案的核心優勢是大大減少了元件數量,從而提高了效率,簡化了生產并減少了電路板占位空間。

總之,隨著更多系統級設計需要滿足更加嚴格的規范,盡可能充分利用模塊化電源設計變得至關重要,尤其在電源設計專業經驗有限的情況下。由于許多細分市場要求系統設計必須符合最新的EMI規范要求,因此將Silent Switcher技術運用于小尺寸設計,同時借助µModule穩壓器簡單易用的特性,可以大大縮短產品上市時間,同時還可以節省電路板空間。

Silent Switcher µModule穩壓器的優勢

參考文獻

1 Aldrick Limjoco、Patrick Pasaquian和Jefferson Eco,“Silent Switcher µModule穩壓器為GSPS采樣ADC提供低噪聲供電,并節省一半空間”ADI公司,2018年10月。

作者簡介

BhakTI Waghmare現任Power by Linear產品部μModule穩壓器的產品營銷工程師,工作地點在美國加利福尼亞州圣克拉拉市。她負責μModule穩壓器電源產品的市場營銷支持。Bhakti于2018年加入ADI公司。她擁有韋恩州立大學(位于美國密歇根州底特律)機械工程學士學位和工業工程碩士學位。

作者簡介

Diarmuid Carey是歐洲中央應用中心的應用工程師,工作地點在愛爾蘭利默里克。他自2008年以來一直擔任應用工程師,并于2017年加入ADI公司,為歐洲的眾多市場客戶提供Power by Linear產品組合的設計支持。他擁有利默里克大學計算機工程學士學位。