一、概述

本文介紹一種采用MAX7348的串行I2C總線的鍵盤電路以及驅動程序的設計。

I2C 需要連線少,僅需一條串行時鐘線和一條串行數(shù)據(jù)線。允許多主機控制,具有裁決和同步功能,可隨意添加或摘除總線上的子器件等諸多優(yōu)點,所以已經(jīng)被廣泛應用。

二、MAX7348

MAX7348 是美國MAXIM 公司生產(chǎn)的2 線接口、低EMI 鍵盤開關和發(fā)聲控制器,可監(jiān)控多達40 個按鍵,可對按鍵去抖并保存在FIFO 中,去抖時間用戶可在9 ~ 40ms 之間任意設置,MAX7348 自帶的音調(diào)發(fā)生器在控制器的作用下可自動發(fā)出按鍵聲和報警聲,在發(fā)聲期間,輸出還可以設置為高電平或低電平,以驅動電子發(fā)聲器、繼電器或指示燈。

芯片采用400Kps,5.5V 容限2 線串行接口,工作電壓2.4 ~ 3.6V,4 個I2C 地址選擇。與MAX7348同系列的還有MAX7347 和MAX7349 等。

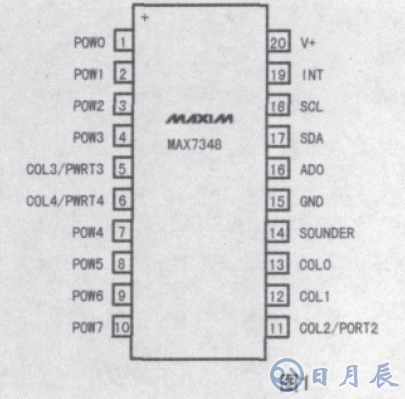

如圖1 所示,SDA 、SCL 分別是兼容I2C 串行總線的數(shù)據(jù)、時鐘接口,使用時通常需要接一個典型值為4.7kΩ 的上拉電阻;ROW0 ~ ROW8 為鍵盤矩陣行輸入端口,不用時開路;COL0 ~ COL4為鍵盤矩陣列輸出端口;SOUNDER 為發(fā)聲器輸出端口,該輸出為推挽結構,通常與地之間接一個壓電陶瓷片或其他發(fā)聲設備;INT 為中斷輸出端口;ADO 為地址輸入端口,用來設置器件的從地址,該引腳接GND、V+、SDA、SCL 可形成4 種邏輯組合構成MAX7348 的4 個可選的I2C 地址,如表1 ;GND 為接地端,V+ 接電源(2.4 ~ 3.6V)。

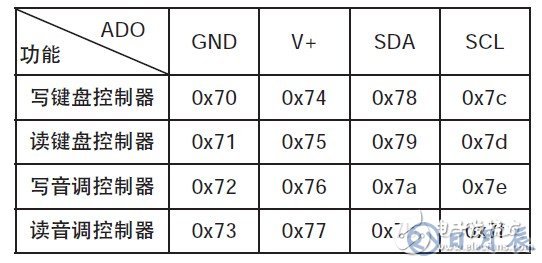

表1 2線接口地址分配表

D0 ~ D5 位表示按鍵中的那些鍵已去抖,D6 指明當前去抖按鍵是否是FIFO 中的最后一個;D7 位是溢出標志,它表示按鍵FIFO 是否溢出。讀按鍵掃描FIFO 將清除中斷信號,但是只有通過執(zhí)行足夠次數(shù)的讀操作清空FIFO后才能再次產(chǎn)生中斷(INT)信號。

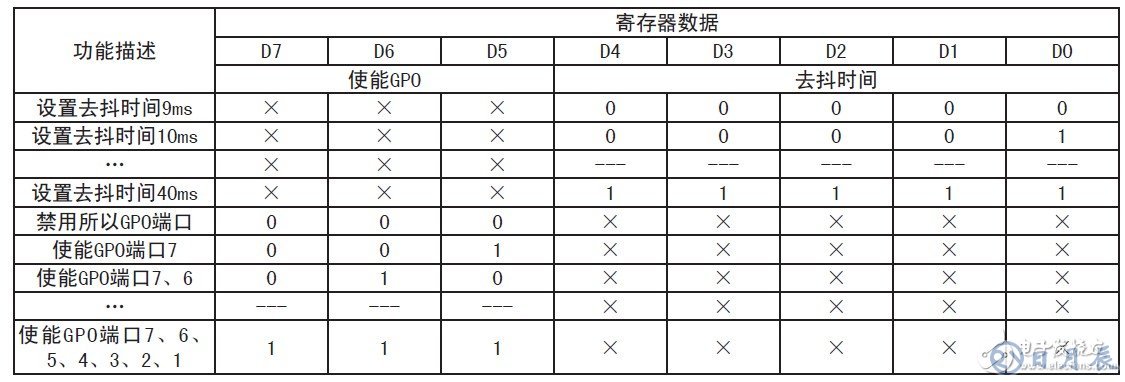

(2)去抖寄存器( 01H) 該寄存器用來設置每一個去抖周期的時間,以及使能和禁用GPO 端口,其中D0 ~ D4 位用來在9 ~ 40ms 范圍內(nèi)設置去抖時間,步長1ms,D5 ~ D7 用來設置使能那一個GPO 端口(表2)。

表2 去抖寄存器設置

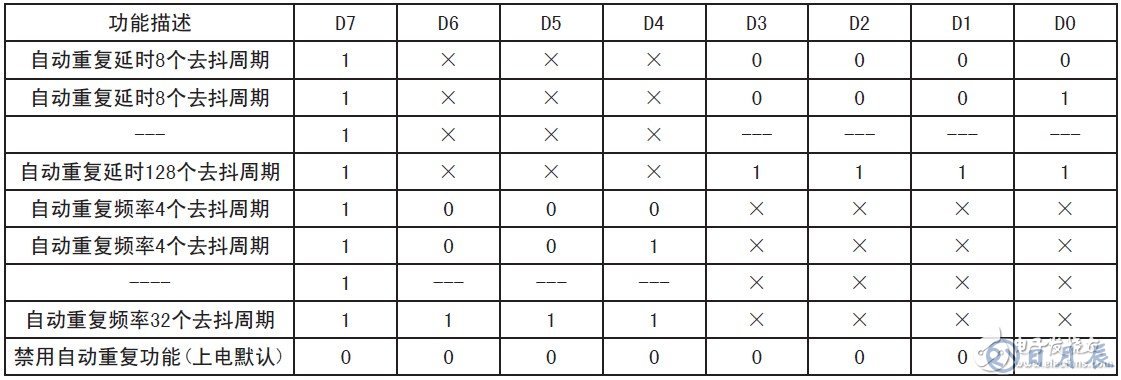

(3)自動重復寄存器( 02H)該寄存器用來設置自動重復頻率及其延時。當按鍵按下且沒有釋放時,自動重復功能允許連續(xù)觸發(fā)按鍵事件。自動重復延時規(guī)定了第一次按下按鍵與開始重復之間的時間(如果按鍵沒有釋放)。自動重復頻率規(guī)定了自動重復開始后按鍵事件連續(xù)觸發(fā)的速度。D0 ~ D3設定自動重復延時,范圍從8 個去抖周期到128 個去抖周期。D4 ~ D6 位規(guī)定重復頻率,范圍是4 到32 個去抖周期,D7 位是自動重復功能使能位(如表3 所示)。

表3 自動重復寄存器

(4) 中斷寄存器( 03H) 該寄存器包含與中斷請求功能設置有關的信息,以及INT 輸出的狀態(tài),INT 輸出也可配置為GPO.中斷寄存器是只讀寄存器,向該寄存器寫入數(shù)據(jù)無效。

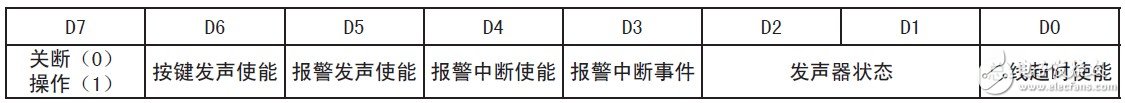

(5)配置寄存器(04H)該寄存器反映發(fā)聲器的狀態(tài)、控制I2C 總線超時、使能報警輸入中斷、使能發(fā)聲器對報警輸入和按鍵去抖時間做出響應,以及控制器件關斷等。該寄存器結構如表4 所示,除D1、D2 設定發(fā)聲器輸出狀態(tài)外,其余每一位對應一個控制狀態(tài),用戶可根據(jù)需要使能(置"1")或禁止(置"0")。

表4 配置寄存器結構

(6)按鍵發(fā)聲寄存器( 06H) 如果配置寄存器(04H)中使能按鍵發(fā)聲,那么當一個鍵或一組鍵去抖后,發(fā)聲控制器將發(fā)出聲音,并由按鍵發(fā)聲寄存器設定發(fā)聲的時間和頻率。

除以上幾個主要寄存器外還有端口寄存器、報警聲寄存器、發(fā)聲器寄存器等多個寄存器,這些寄存器主要用于控制發(fā)聲器和擴展GPO 端口,在此不做詳細敘述,感興趣的讀者可以自行查閱有關MAX7348 的技術資料。

三、電路設計

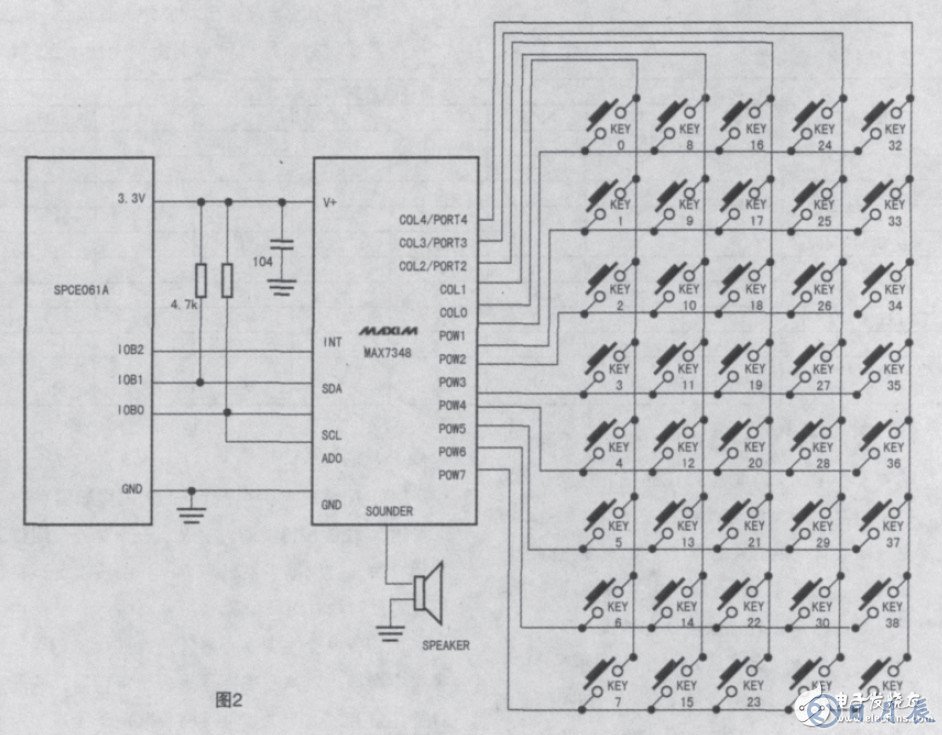

圖2 是筆者設計的MAX7348 應用電路,該電路以凌陽(SPCE061A)單片機為主控制器,結合MAX7348 構成了一個具有40 個按鍵的鍵盤電路,通過程序可以設置按鍵發(fā)聲、自動連續(xù)按鍵、中斷輸出等功能。MAX7348 的SDA、SCL、INT 分別與SPCE061A 單片機的IOB0、IOB1、IOB2(注:SPCE061A 單片機的IOB2 為外部中斷1 的輸入口)連接,由于I2C 總線允許掛接多個從機,所以在實際使用中,可以將多個不同從機地址的設備掛接在同一總線上,為單片機節(jié)約大量的硬件資源。

四、軟件編寫

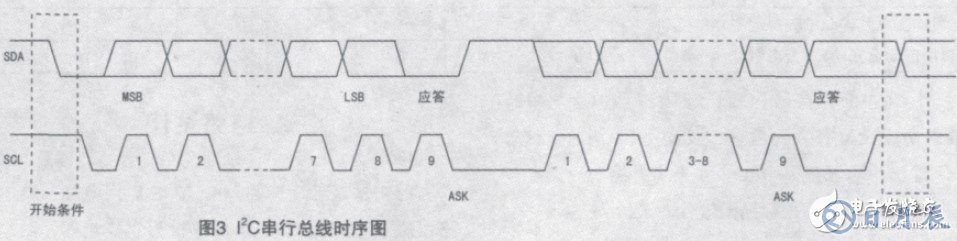

在圖2 所示的鍵盤電路中,由于MAX7348 只具有兼容的I2C 接口,而SPCE061A 單片機本身不具備I2C接口,要實現(xiàn)二者之間的數(shù)據(jù)傳輸,通常采用通用IO口軟件模擬I2C 的方式來實現(xiàn)。圖3 是MAX7348 的總線時序。

由圖3 所示的時序圖可以看出,用軟件模擬I2C 總線的傳輸時序,大致要經(jīng)歷構造開始條件、發(fā)送從機地址(含讀寫標志位)、等待從機響應、發(fā)送(或讀取)1 個字節(jié)數(shù)據(jù)(或命令)。

筆者編寫的模擬I2C 總線驅動程序,經(jīng)過多次調(diào)試,程序符合I2C 總線傳輸時序要求,與I2C總線設備通訊可靠,但需要注意的一點是:以上代碼是在SPCE061A 單片機默認時鐘頻率(24M)的情況下編寫的,如果采用較高的系統(tǒng)時鐘,需要在部分代碼中間添加一些延時程序,否則會出現(xiàn)數(shù)據(jù)丟失,造成通訊錯誤。

五、小結

本文介紹的MAX7348 與單片機的接口具有電路簡單,易于實現(xiàn),節(jié)省了單片機的IO 口,提高了鍵盤電路的穩(wěn)定性和可靠性,在筆者制作的5 層電梯模型中工作穩(wěn)定,性能可靠,是一種值得推廣的鍵盤擴展方案,可應用在工業(yè)控制、PDA、醫(yī)療器械等多個領域。