在完成MOS管芯片在制作之后,需要給MOS管芯片加上一個(gè)外殼,這就是MOS管封裝。該封裝外殼主要起著支撐、保護(hù)和冷卻的作用,同時(shí)還可為芯片提供電氣連接和隔離,從而將MOS管器件與其它元件構(gòu)成完整的電路。

而不同的封裝、不同的設(shè)計(jì),MOS管的規(guī)格尺寸、各類電性參數(shù)等都會(huì)不一樣,而它們?cè)陔娐分兴芷鸬降淖饔靡矔?huì)不一樣;另外,封裝還是電路設(shè)計(jì)中MOS管選擇的重要參考。封裝的重要性不言而喻。

MOS管封裝分類

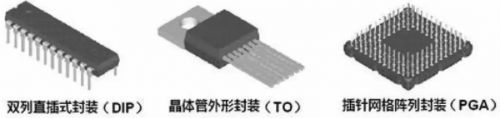

按照安裝在pcb板上的方式來劃分,MOS管封裝主要有兩大類:插入式(Through Hole)和表面貼裝式(Surface Mount)。

插入式就是Mosfet的管腳穿過pcb板的安裝孔并焊接在PCB板上。常見的插入式封裝有:雙列直插式封裝(dip)、晶體管外形封裝(TO)、插針網(wǎng)格陣列封裝(PGA)三種樣式。

插入式封裝

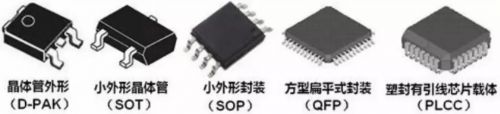

表面貼裝則是MOSFET的管腳及散熱法蘭焊接在PCB板表面的焊盤上。典型表面貼裝式封裝有:晶體管外形(D-PAK)、小外形晶體管(SOT)、小外形封裝(SOP)、方形扁平式封裝(QFP)、塑封有引線芯片載體(plcC)等。

表面貼裝式封裝

隨著技術(shù)的發(fā)展,目前主板、顯卡等的PCB板采用直插式封裝方式的越來越少,更多地選用了表面貼裝式封裝方式。

1、雙列直插式封裝(DIP)

DIP封裝有兩排引腳,需要插入到具有DIP結(jié)構(gòu)的芯片插座上,其派生方式為SDIP(Shrink DIP),即緊縮雙入線封裝,較DIP的針腳密度高6倍。

DIP封裝結(jié)構(gòu)形式有:多層陶瓷雙列直插式DIP、單層陶瓷雙列直插式DIP、引線框架式DIP(含玻璃陶瓷封接式、塑料包封結(jié)構(gòu)式、陶瓷低熔玻璃封裝式)等。DIP封裝的特點(diǎn)是可以很方便地實(shí)現(xiàn)PCB板的穿孔焊接,和主板有很好的兼容性。

但由于其封裝面積和厚度都比較大,而且引腳在插拔過程中很容易被損壞,可靠性較差;同時(shí)由于受工藝的影響,引腳一般都不超過100個(gè),因此在電子產(chǎn)業(yè)高度集成化過程中,DIP封裝逐漸退出了歷史舞臺(tái)。

2、晶體管外形封裝(TO)

屬于早期的封裝規(guī)格,例如TO-3P、TO-247、TO-92、TO-92L、TO-220、TO-220F、TO-251等都是插入式封裝設(shè)計(jì)。

TO-3P/247:是中高壓、大電流MOS管常用的封裝形式,產(chǎn)品具有耐壓高、抗擊穿能力強(qiáng)等特點(diǎn)。

TO-220/220F:TO-220F是全塑封裝,裝到散熱器上時(shí)不必加絕緣墊;TO-220帶金屬片與中間腳相連,裝散熱器時(shí)要加絕緣墊。這兩種封裝樣式的MOS管外觀差不多,可以互換使用。

TO-251:該封裝產(chǎn)品主要是為了降低成本和縮小產(chǎn)品體積,主要應(yīng)用于中壓大電流60A以下、高壓7N以下環(huán)境中。

TO-92:該封裝只有低壓MOS管(電流10A以下、耐壓值60V以下)和高壓1N60/65在采用,目的是降低成本。

近年來,由于插入式封裝工藝焊接成本高、散熱性能也不如貼片式產(chǎn)品,使得表面貼裝市場需求量不斷增大,也使得TO封裝發(fā)展到表面貼裝式封裝。TO-252(又稱之為D-PAK)和TO-263(D2PAK)就是表面貼裝封裝。

TO封裝產(chǎn)品外觀

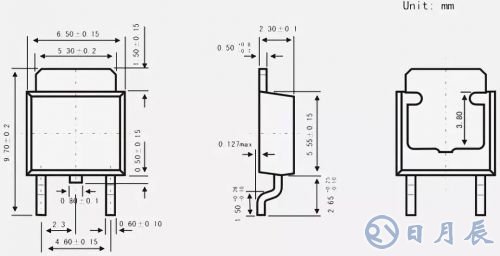

TO252/D-PAK是一種塑封貼片封裝,常用于功率晶體管、穩(wěn)壓芯片的封裝,是目前主流封裝之一。

采用該封裝方式的MOSFET有3個(gè)電極,柵極(G)、漏極(D)、源極(S)。

其中漏極(D)的引腳被剪斷不用,而是使用背面的散熱板作漏極(D),直接焊接在PCB上,一方面用于輸出大電流,一方面通過PCB散熱;所以PCB的D-PAK焊盤有三處,漏極(D)焊盤較大。其封裝規(guī)范如下:

TO-252/D-PAK封裝尺寸規(guī)格

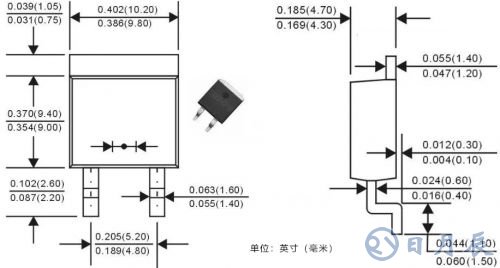

TO-263是TO-220的一個(gè)變種,主要是為了提高生產(chǎn)效率和散熱而設(shè)計(jì),支持極高的電流和電壓,在150A以下、30V以上的中壓大電流MOS管中較為多見。

除了D2PAK(TO-263AB)之外,還包括TO263-2、TO263-3、TO263-5、TO263-7等樣式,與TO-263為從屬關(guān)系,主要是引出腳數(shù)量和距離不同。

TO-263/D2PAK封裝尺寸規(guī)格

3、插針網(wǎng)格陣列封裝(PGA)

PGA(PIn Grid Array Package)芯片內(nèi)外有多個(gè)方陣形的插針,每個(gè)方陣形插針沿芯片的四周間隔一定距離排列,根據(jù)管腳數(shù)目的多少,可以圍成2~5圈。安裝時(shí),將芯片插入專門的PGA插座即可,具有插拔方便且可靠性高的優(yōu)勢,能適應(yīng)更高的頻率。

PGA封裝樣式

其芯片基板多數(shù)為陶瓷材質(zhì),也有部分采用特制的塑料樹脂來做基板,在工藝上,引腳中心距通常為2.54mm,引腳數(shù)從64到447不等。

這種封裝的特點(diǎn)是,封裝面積(體積)越小,能夠承受的功耗(性能)就越低,反之則越高。這種封裝形式芯片在早期比較多見,且多用于cpu等大功耗產(chǎn)品的封裝,如英特爾的80486、Pentium均采用此封裝樣式;不大為MOS管廠家所采納。

4、小外形晶體管封裝(SOT)

SOT(Small Out-Line Transistor)是貼片型小功率晶體管封裝,主要有SOT23、SOT89、SOT143、SOT25(即SOT23-5)等,又衍生出SOT323、SOT363/SOT26(即SOT23-6)等類型,體積比TO封裝小。

SOT封裝類型

SOT23是常用的三極管封裝形式,有3條翼形引腳,分別為集電極、發(fā)射極和基極,分別列于元件長邊兩側(cè),其中,發(fā)射極和基極在同一側(cè),常見于小功率晶體管、場效應(yīng)管和帶電阻網(wǎng)絡(luò)的復(fù)合晶體管,強(qiáng)度好,但可焊性差,外形如下圖(a)所示。

SOT89具有3條短引腳,分布在晶體管的一側(cè),另外一側(cè)為金屬散熱片,與基極相連,以增加散熱能力,常見于硅功率表面組裝晶體管,適用于較高功率的場合,外形如下圖(b)所示。

SOT143具有4條翼形短引腳,從兩側(cè)引出,引腳中寬度偏大的一端為集電極,這類封裝常見于高頻晶體管,外形如下圖(c)所示。

SOT252屬于大功率晶體管,3條引腳從一側(cè)引出,中間一條引腳較短,為集電極,與另一端較大的引腳相連,該引腳為散熱作用的銅片,外形如下圖(d)所示。

常見SOT封裝外形比較

主板上常用四端引腳的SOT-89 MOSFET。其規(guī)格尺寸如下:

SOT-89 MOSFET尺寸規(guī)格(單位:mm)

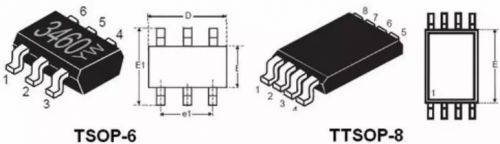

5、小外形封裝(SOP)

SOP(Small Out-Line Package)是表面貼裝型封裝之一,也稱之為SOL或DFP,引腳從封裝兩側(cè)引出呈海鷗翼狀(L字形)。材料有塑料和陶瓷兩種。

SOP封裝標(biāo)準(zhǔn)有SOP-8、SOP-16、SOP-20、SOP-28等,SOP后面的數(shù)字表示引腳數(shù)。MOSFET的SOP封裝多數(shù)采用SOP-8規(guī)格,業(yè)界往往把“P”省略,簡寫為SO(Small Out-Line)。

SOP-8封裝尺寸

SO-8為PHILIP公司率先開發(fā),采用塑料封裝,沒有散熱底板,散熱不良,一般用于小功率MOSFET。

后逐漸派生出TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)等標(biāo)準(zhǔn)規(guī)格;其中TSOP和TSSOP常用于MOSFET封裝。

常用于MOS管的SOP派生規(guī)格

6、方形扁平式封裝(QFP)

QFP(Plastic Quad Flat Package)封裝的芯片引腳之間距離很小,管腳很細(xì),一般在大規(guī)模或超大型集成電路中采用,其引腳數(shù)一般在100個(gè)以上。

用這種形式封裝的芯片必須采用smt表面安裝技術(shù)將芯片與主板焊接起來。該封裝方式具有四大特點(diǎn):

①適用于SMD表面安裝技術(shù)在pcb電路板上安裝布線;

②適合高頻使用;

③操作方便,可靠性高;

④芯片面積與封裝面積之間的比值較小。

與PGA封裝方式一樣,該封裝方式將芯片包裹在塑封體內(nèi),無法將芯片工作時(shí)產(chǎn)生的熱量及時(shí)導(dǎo)出,制約了MOSFET性能的提升;而且塑封本身增加了器件尺寸,不符合半導(dǎo)體向輕、薄、短、小方向發(fā)展的要求;另外,此類封裝方式是基于單顆芯片進(jìn)行,存在生產(chǎn)效率低、封裝成本高的問題。

因此,QFP更適于微處理器/門陳列等數(shù)字邏輯LSI電路采用,也適于VTR信號(hào)處理、音響信號(hào)處理等模擬LSI電路產(chǎn)品封裝。

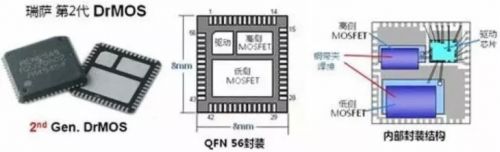

7、四邊無引線扁平封裝(QFN)

QFN(Quad Flat Non-leaded package)封裝四邊配置有電極接點(diǎn),由于無引線,貼裝表現(xiàn)出面積比QFP小、高度比QFP低的特點(diǎn);其中陶瓷QFN也稱為LCC(Leadless Chip Carriers),采用玻璃環(huán)氧樹脂印刷基板基材的低成本塑料QFN則稱為塑料LCC、PCLC、P-LCC等。

是一種焊盤尺寸小、體積小、以塑料作為密封材料的新興表面貼裝芯片封裝技術(shù)。

QFN主要用于集成電路封裝,MOSFET不會(huì)采用。不過因INTEL提出整合驅(qū)動(dòng)與MOSFET方案,而推出了采用QFN-56封裝(“56”指芯片背面有56個(gè)連接Pin)的DrMOS。

需要說明的是,QFN封裝與超薄小外形封裝(TSSOP)具有相同的外引線配置,而其尺寸卻比TSSOP的小62%。根據(jù)QFN建模數(shù)據(jù),其熱性能比TSSOP封裝提高了55%,電性能(電感和電容)比TSSOP封裝分別提高了60%和30%。最大的缺點(diǎn)則是返修難度高。

采用QFN-56封裝的DrMOS

傳統(tǒng)的分立式dc/dc降壓開關(guān)電源無法滿足對(duì)更高功耗密度的要求,也不能解決高開關(guān)頻率下的寄生參數(shù)影響問題。

隨著技術(shù)的革新與進(jìn)步,把驅(qū)動(dòng)器和MOSFET整合在一起,構(gòu)建多芯片模塊已經(jīng)成為了現(xiàn)實(shí),這種整合方式同時(shí)可以節(jié)省相當(dāng)可觀的空間從而提升功耗密度,通過對(duì)驅(qū)動(dòng)器和MOS管的優(yōu)化提高電能效率和優(yōu)質(zhì)DC電流,這就是整合驅(qū)動(dòng)IC的DrMOS。

瑞薩第2代DrMOS

經(jīng)過QFN-56無腳封裝,讓DrMOS熱阻抗很低;借助內(nèi)部引線鍵合以及銅夾帶設(shè)計(jì),可最大程度減少外部PCB布線,從而降低電感和電阻。

另外,采用的深溝道硅(trench silicon)MOSFET工藝,還能顯著降低傳導(dǎo)、開關(guān)和柵極電荷損耗;并能兼容多種控制器,可實(shí)現(xiàn)不同的工作模式,支持主動(dòng)相變換模式APS(Auto Phase Switching)。

除了QFN封裝外,雙邊扁平無引腳封裝(DFN)也是一種新的電子封裝工藝,在安森美的各種元器件中得到了廣泛采用,與QFN相比,DFN少了兩邊的引出電極。

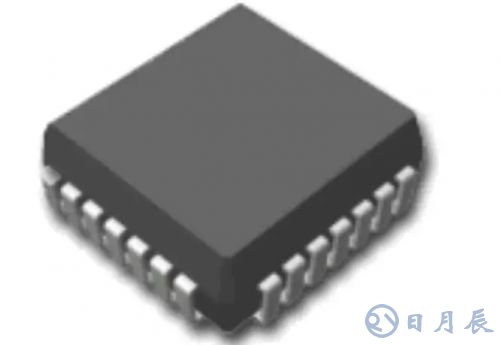

8、塑封有引線芯片載體(PLCC)

PLCC(Plastic Quad Flat Package)外形呈正方形,尺寸比DIP封裝小得多,有32個(gè)引腳,四周都有管腳,引腳從封裝的四個(gè)側(cè)面引出,呈丁字形,是塑料制品。

其引腳中心距1.27mm,引腳數(shù)從18到84不等,J形引腳不易變形,比QFP容易操作,但焊接后的外觀檢查較為困難。PLCC封裝適合用SMT表面安裝技術(shù)在PCB上安裝布線,具有外形尺寸小、可靠性高的優(yōu)點(diǎn)。

PLCC封裝是比較常見,用于邏輯LSI、DLD(或程邏輯器件)等電路,主板BiOs常采用的這種封裝形式,不過目前在MOS管中較少見。

PLCC封裝樣式

主流企業(yè)的封裝與改進(jìn)

由于CPU的低電壓、大電流的發(fā)展趨勢,對(duì)MOSFET提出輸出電流大,導(dǎo)通電阻低,發(fā)熱量低散熱快,體積小的要求。MOSFET廠商除了改進(jìn)芯片生產(chǎn)技術(shù)和工藝外,也不斷改進(jìn)封裝技術(shù),在與標(biāo)準(zhǔn)外形規(guī)格兼容的基礎(chǔ)上,提出新的封裝外形,并為自己研發(fā)的新封裝注冊(cè)商標(biāo)名稱。

1、瑞薩(RENESAS)WPAK、LFPAK和LFPAK-I封裝

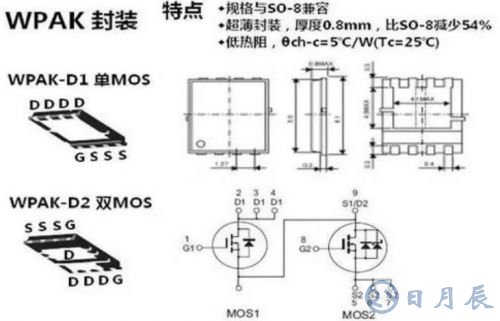

WPAK是瑞薩開發(fā)的一種高熱輻射封裝,通過仿D-PAK封裝那樣把芯片散熱板焊接在主板上,通過主板散熱,使小形封裝的WPAK也可以達(dá)到D-PAK的輸出電流。WPAK-D2封裝了高/低2顆MOSFET,減小布線電感。

瑞薩WPAK封裝尺寸

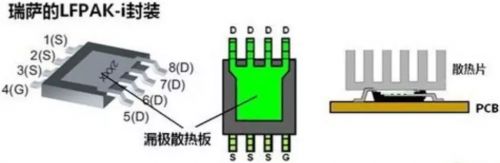

LFPAK和LFPAK-I是瑞薩開發(fā)的另外2種與SO-8兼容的小形封裝。LFPAK類似D-PAK,但比D-PAK體積小。LFPAK-i是將散熱板向上,通過散熱片散熱。

瑞薩LFPAK和LFPAK-I封裝

2、威世(VISHAY)Power-PAK和Polar-PAK封裝

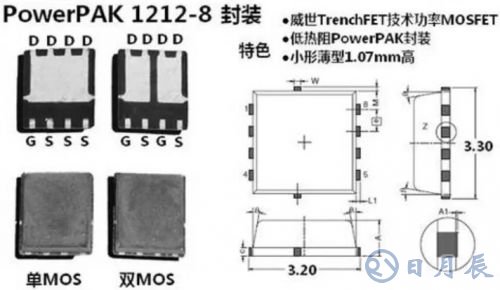

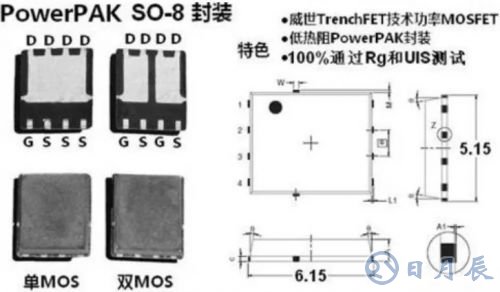

Power-PAK是威世公司注冊(cè)的MOSFET封裝名稱。Power-PAK包括有Power-PAK1212-8、Power-PAK SO-8兩種規(guī)格。

威世Power-PAK1212-8封裝

威世Power-PAK SO-8封裝

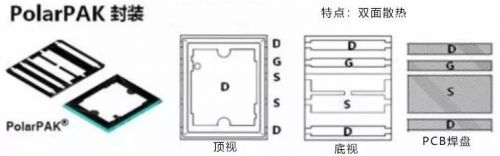

Polar PAK是雙面散熱的小形封裝,也是威世核心封裝技術(shù)之一。Polar PAK與普通的so-8封裝相同,其在封裝的上、下兩面均設(shè)計(jì)了散熱點(diǎn),封裝內(nèi)部不易蓄熱,能夠?qū)⒐ぷ麟娏鞯碾娏髅芏忍岣咧罶O-8的2倍。目前威世已向意法半導(dǎo)體公司提供Polar PAK技術(shù)授權(quán)。

威世Polar PAK封裝

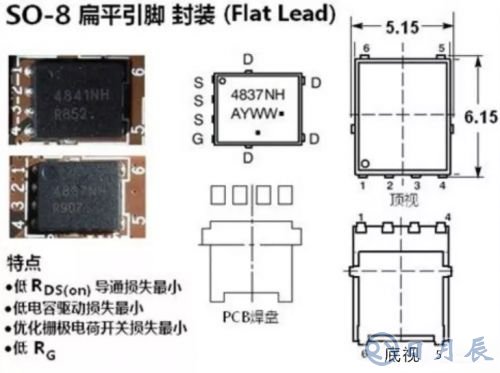

3、安森美(Onsemi)SO-8和WDFN8扁平引腳(Flat Lead)封裝

安美森半導(dǎo)體開發(fā)了2種扁平引腳的MOSFET,其中SO-8兼容的扁平引腳被很多板卡采用。安森美新近推出的NVMx和NVTx功率MOSFET就采用了緊湊型DFN5(SO-8FL)和WDFN8封裝,可最大限度地降低導(dǎo)通損耗,另外還具有低QG和電容,可將驅(qū)動(dòng)器損耗降到最低的特性。

安森美SO-8扁平引腳封裝

安森美WDFN8封裝

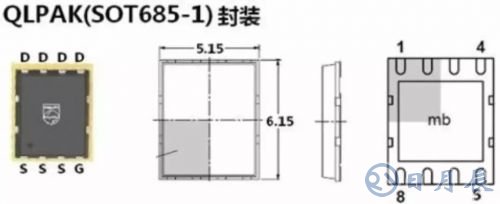

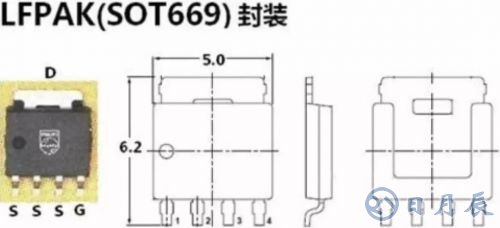

4、恩智浦(NXP)LFPAK和QLPAK封裝

恩智浦(原Philps)對(duì)SO-8封裝技術(shù)改進(jìn)為LFPAK和QLPAK。其中LFPAK被認(rèn)為是世界上高度可靠的功率SO-8封裝;而QLPAK具有體積小、散熱效率更高的特點(diǎn),與普通SO-8相比,QLPAK占用PCB板的面積為6*5mm,同時(shí)熱阻為1.5k/W。

恩智浦LFPAK封裝

恩智浦QLPAK封裝

5、意法(ST)半導(dǎo)體PowerSO-8封裝

意法半導(dǎo)體功率MOSFET芯片封裝技術(shù)有SO-8、PowerSO-8、PowerFLAT、DirectFET、PolarPAK等,其中PowerSO-8正是SO-8的改進(jìn)版,此外還有PowerSO-10、PowerSO-20、TO-220FP、H²PAK-2等封裝。

意法半導(dǎo)體Power SO-8封裝

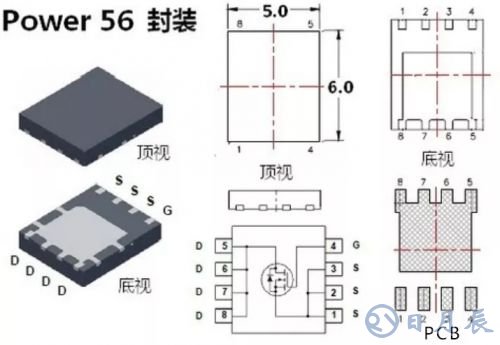

6、飛兆(FAIRCHILD)半導(dǎo)體Power 56封裝

Power 56是Farichild的專用稱呼,正式名稱為DFN 5×6。其封裝面積跟常用的TSOP-8不相上下,而薄型封裝又節(jié)約元件凈空高度,底部Thermal-Pad設(shè)計(jì)降低了熱阻,因此很多功率器件廠商都部署了DFN 5×6。

FAIrchild Power 56封裝

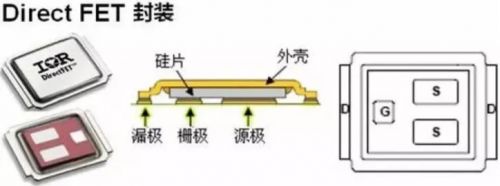

7、國際整流器(IR)Direct FET封裝

Direct FET能在SO-8或更小占位面積上,提供高效的上部散熱,適用于計(jì)算機(jī)、筆記本電腦、電信和消費(fèi)電子設(shè)備的AC-DC及DC-DC功率轉(zhuǎn)換應(yīng)用。與標(biāo)準(zhǔn)塑料分立封裝相比,DirectFET的金屬罐構(gòu)造具有雙面散熱功能,因而可有效將高頻DC-DC降壓式轉(zhuǎn)換器的電流處理能力增加一倍。

Direct FET封裝屬于反裝型,漏極(D)的散熱板朝上,并覆蓋金屬外殼,通過金屬外殼散熱。Direct FET封裝極大地改善了散熱,并且占用空間更小,散熱良好。

國際整流器Direct FET封裝

IR Direct FET封裝系列部分產(chǎn)品規(guī)格

內(nèi)部封裝改進(jìn)方向

除了外部封裝,基于電子制造對(duì)MOS管的需求的變化,內(nèi)部封裝技術(shù)也在不斷得到改進(jìn),這主要從三個(gè)方面進(jìn)行:改進(jìn)封裝內(nèi)部的互連技術(shù)、增加漏極散熱板、改變散熱的熱傳導(dǎo)方向。

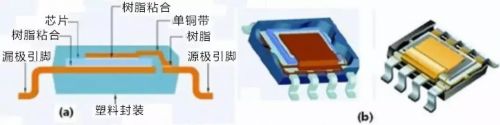

1、封裝內(nèi)部的互連技術(shù)

TO、D-PAK、SOT、SOP等采用焊線式的內(nèi)部互連封裝技術(shù),當(dāng)CPU或gpu供電發(fā)展到低電壓、大電流時(shí)代,焊線式的SO-8封裝就受到了封裝電阻、封裝電感、pn結(jié)到PCB和外殼熱阻等因素的限制。

SO-8內(nèi)部封裝結(jié)構(gòu)

這四種限制對(duì)其電學(xué)和熱學(xué)性能有著極大的影響。隨著電流密度的提高,MOSFET廠商在采用SO-8尺寸規(guī)格時(shí),同步對(duì)焊線互連形式進(jìn)行了改進(jìn),用金屬帶、或金屬夾板代替焊線,以降低封裝電阻、電感和熱阻。

標(biāo)準(zhǔn)型SO-8與無導(dǎo)線SO-8封裝對(duì)比

國際整流器(IR)的改進(jìn)技術(shù)稱之為Copper Strap;威世(Vishay)稱之為Power Connect技術(shù);飛兆半導(dǎo)體則叫做Wireless Package。新技術(shù)采用銅帶取代焊線后,熱阻降低了10-20%,源極至封裝的電阻降低了61%。

國際整流器的Copper Strap技術(shù)

威世的Power Connect技術(shù)

飛兆半導(dǎo)體的Wirless Package技術(shù)

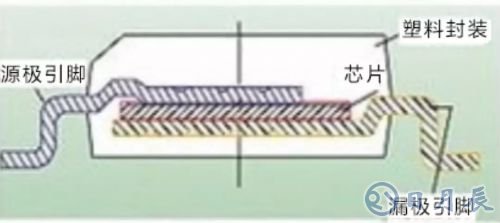

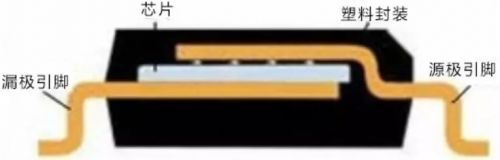

2、增加漏極散熱板

標(biāo)準(zhǔn)的SO-8封裝采用塑料將芯片包圍,低熱阻的熱傳導(dǎo)通路只是芯片到PCB的引腳。而底部緊貼PCB的塑料外殼是熱的不良導(dǎo)體,故而影響了漏極的散熱。

技術(shù)改進(jìn)就是要除去引線框下方的塑封化合物,方法是讓引線框金屬結(jié)構(gòu)直接或加一層金屬板與PCB接觸,并焊接到PCB焊盤上,這樣就提供了更多的散熱接觸面積,把熱量從芯片上帶走;同時(shí)也可以制成更薄的器件。

威世Power-PAK技術(shù)

威世的Power-PAK、法意半導(dǎo)體的Power SO-8、安美森半導(dǎo)體的SO-8 Flat Lead、瑞薩的WPAK/LFPAK、飛兆半導(dǎo)體的Power 56和Bottomless Package都采用了此散熱技術(shù)。

3、改變散熱的熱傳導(dǎo)方向

Power-PAK的封裝雖然顯著減小了芯片到PCB的熱阻,但當(dāng)電流需求繼續(xù)增大時(shí),PCB同時(shí)會(huì)出現(xiàn)熱飽和現(xiàn)象。所以散熱技術(shù)的進(jìn)一步改進(jìn)就是改變散熱方向,讓芯片的熱量傳導(dǎo)到散熱器而不是PCB。

瑞薩LFPAK-i封裝

瑞薩的LFPAK-I封裝、國際整流器的Direct FET封裝均是這種散熱技術(shù)的典型代表。

總結(jié)

未來,隨著電子制造業(yè)繼續(xù)朝著超薄、小型化、低電壓、大電流方向的發(fā)展,MOS管的外形及內(nèi)部封裝結(jié)構(gòu)也會(huì)隨之改變,以更好適應(yīng)制造業(yè)的發(fā)展需求。另外,為降低電子制造商的選用門檻,MOS管向模塊化、系統(tǒng)級(jí)封裝方向發(fā)展的趨勢也將越來越明顯,產(chǎn)品將從性能、成本等多維度協(xié)調(diào)發(fā)展。

而封裝作為MOS管選型的重要參考因素之一,不同的電子產(chǎn)品有不同的電性要求,不同的安裝環(huán)境也需要匹配的尺寸規(guī)格來滿足。實(shí)際選用中,應(yīng)在大原則下,根據(jù)實(shí)際需求情況來做抉擇。

有些電子系統(tǒng)受制于PCB的尺寸和內(nèi)部的高度,如通信系統(tǒng)的模塊電源由于高度的限制通常采用DFN5*6、DFN3*3的封裝;在有些ACDC的電源中,使用超薄設(shè)計(jì)或由于外殼的限制,適于裝配TO220封裝的功率MOS管,此時(shí)引腳可直接插到根部,而不適于使用TO247封裝的產(chǎn)品;也有些超薄設(shè)計(jì)需要將器件管腳折彎平放,這會(huì)加大MOS管選用的復(fù)雜度。