儀表放大器是在有噪聲的環境下放大小信號的器件。它利用的是差分小信號疊加在較大的共模信號之上的特性,能夠去除共模信號,而又同時將差分信號放大。儀表放大器的關鍵參數是共模抑制比,這個性能可以用來衡量差分增益與共模衰減之比。

典型的被測信號可以是生物信號,如心電圖(ECG)信號或者是來自諸如惠斯登電橋等傳感器的微弱信號。由于這些信號源常常具有幾千歐姆或更高的輸出阻抗,因此儀表放大器需要具有很高的輸入阻抗(典型數值在千兆歐姆級)。此外,由于儀表放大器往往要驅動輸入阻抗很低的后級電路,如A/D轉換器等,因此要求儀表放大器的輸出阻抗很低。儀表放大器工作頻率通常在直流到1 MHz之間,而在MHz級的速度下,輸入電容比輸入電阻更為重要,因此這類應用要考慮使用差分放大器。這種差分放大器輸入阻抗較低,但速度要快很多。

常見儀表放大器

差動放大器

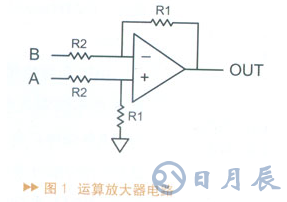

差動放大器不是儀表放大器,但是有時可以用在儀表放大器的場合。其電路只需一個運算放大器,如圖1所示。在對高輸入阻抗或者增益沒有苛刻要求的場合,使用它是很方便的。

該電路的傳遞函數為:

Vout=R1/R2(VA-VB)

這一傳遞函數是在理想運算放大器和理想電阻器匹配條件下得出的。然而,當電阻不完全匹配時,同相放大電路和反相放大電路的傳遞函數不相等,就會有共模信號泄露出來。以0.1%的電阻匹配誤差為例,最差情況下CMRR為54 dB,即10 V的共模信號會產生20 mV的輸出誤差。

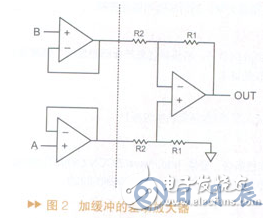

差動放大器的優點是結構簡單,最主要的缺點是輸入阻抗很低。由于增益由R1/R2決定,因此需要在高增益和高輸入阻抗間做出折中。此外,將信號分壓變小后再進行放大(如同相通路),并不是獲得良好噪聲性能的方法。對于反相通路而言,加入了額外的電阻,并且反相放大電路的噪聲增益總比信號增益高。提高輸入阻抗就要求增加電阻的數值,這樣將會產生更多的噪聲。最后,共模抑制比也受到限制。為了改善這些缺點,第一步是對輸入進行緩沖,這樣就解決了輸入阻抗的問題,如圖2所示。

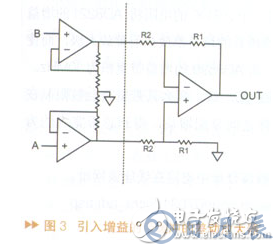

在對輸入進行緩沖的同時,如果引入一些增益,除了可以得到高阻抗,還會產生很好的噪聲性能,如圖3所示。

電路中差動放大器的噪聲仍然存在,但折算到輸入端時噪聲要除以第一級的增益。由于可以使用阻值非常小的電阻器,因此第一級的噪聲可以做得非常低,而且不影響輸入阻抗。這種結構的另外一個好處是在高增益時有較寬的帶寬。原因是電壓反饋放大器具有一定的增益帶寬乘積,通過把增益分散到兩級放大器,可使每一級的增益比較低,降低差動放大器級的增益,從而不會被增益帶寬乘積所限制。然而還有一個沒解決的問題就是共模抑制比。圖3的電路將共模信號和差分信號都放大了,而所有的共模抑制都在差分放大級實現,因此,很容易超過第一級的輸入電壓范圍。

三運放儀表放大器

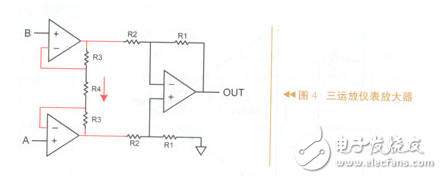

將圖3中第一級放大電路中的接地點去掉來解決共模抑制的問題,從而構成三運放結構儀表放大器,如圖4所示。

第一級電路讓共模信號有效地通過,沒有任何放大或衰減,第二級差動放大器將共模信號去除。由于額外提升了差分增益,雖然電阻器的匹配狀況并沒有改善,但是系統的有效共模抑制能力卻得到了增強。在實際應用中需要注意:

1)必須在第一級提供增益;

2)系統的共模抑制不是由前兩個放大器的共模抑制比性能決定的,而是取決于兩個共模抑制的匹配程度。然而雙運算放大器從來不會給出這一指標,因此選擇時必須要求CMRR性能指標比需要的目標性能指標至少好6 dB;

3)如果電阻器有某些對地的泄露通路,CMRR指標就會降低;

4)儀表放大器前面的元件要盡可能設計得平衡。如果儀表放大器同相通路中低通濾波器和反相通路中低通濾波器具有不同截止頻率,系統的CMRR特性將會隨著頻率的升高而降低。

對于儀表放大器的第一級,每個運算放大器都要保持其兩個電壓輸入端的電壓相同。圖4中R4兩端的差分電壓應當和兩個輸入端的電壓相同,這個電壓產生一個電流,流過電阻器R3并產生了放大器的增益。

三運放儀表放大器通常會遇到的問題有:

1)這一結構放大差分信號,然后去除共模信號。兩級電路之間的中間節點載荷著大約一半的差分信號再加上共模信號。須確保這個信號處于運放的工作范圍之內。當改變輸入電壓的共模成分時,如果看到類似于飽和的現象,則應首先檢查這里。

2)流過R4的電流。當把儀表放大器的增益設置得很高時,R4就會很小,這意味著差分電壓很大的時候,R4上產生的電流也會相當大。需要檢查這種情況對系統是否有負面作用。

3)反饋通路中的電容。反饋通路的走線應盡可能地短,反饋通路過大的電容在高頻時會使共模抑制比性能降低。

兩運放儀表放大器

如果不需要三運放結構如此高的性能,可使用兩運放結構進行簡化。這種結構的主要優點是結構簡單,它只需要兩個運算放大器和四個電阻器,如圖5所示。由于很少有包含三個運放的器件,因此三運放結構通常需要使用一個四運放器件。而多余的一個運放需要消耗更多的功率,所以兩運放結構在能耗方面也會更低。此外,和三運放結構一樣,兩運放結構電路也具有很高的輸入阻抗。但是兩運放儀表放大器的性能要差一些,通過計算分析,這種結構的共模抑制比對電阻器阻值變化的靈敏度比差分放大器結構略高一些。最壞情況下,對于0.1%的電阻器匹配條件下的CMRR不是54 dB,而是50.5 dB。與三運放儀表放大器不同的是這個CMRR數值不隨增益的增加而改善。由于兩個通路不平衡,同相通路信號的頻率響應與反相通路信號不同。由于反相通路要通過兩級電路而不是一級電路,因此在反相通路中出現了一個相位延遲,并且壓擺率和帶寬特性也會不同,其噪聲性能也會差一些。

兩運放儀表放大器常見的問題是:

1)由于第一級的輸出電壓即放大了的輸入電壓,其中包括共模電壓,因此需要注意第一級的輸出電壓;

2)由于兩運放儀表放大器的CMRR對于電阻的匹配情況極為敏感,因此需要注意電阻器的匹配;

3)高頻性能。因此,對于這三種結構來說:差動放大器 這種放大器很好,也很簡單,只需要一個運算放大器和四個電阻器。然而,它的輸入阻抗與所選電阻器的數值有關,而且噪聲和CMRR的性能也較差。

2)三運放儀表放大器 第一級電路提供高輸入阻抗。當我們在第一級電路中引入增益時,還提高了噪聲和CMRR的性能。

兩運放結構儀表放大器 這種電路結構比三運放結構簡單得多,并且也具有很好的輸入阻抗特性。然而,其噪聲和CMRR性能不能隨著增益的增加而改善。

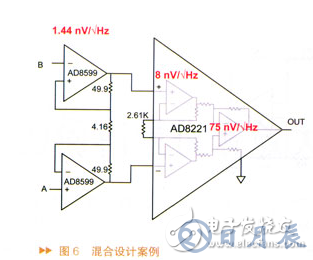

實例分析:混合設計

如果已經找到了基本符合要求的儀表放大器,但某一指標無法滿足需求,此時可以利用現有儀表放大器加上輔助電路達到目的。

噪聲是儀表放大器的一個重要指標,現在很多運放都具有非常低的噪聲系數,如果要求更低的噪聲,則可以采用分立設計方法構建儀表放大器。然而這需要花費很大的精力來設計、布局和調試,而得到的共模抑制比又低于單芯片儀表放大器。圖6所示的混合設計節省了設計時間和電路板空間,同時得到了與單芯片儀表放大器同樣好的共模抑制性能。

這里所示的混合設計分為三級:運放組成的前置放大器,后面是儀表放大器。每一級的噪聲都比前一級大,然而,由于為每一級都分配了增益,所以各級對系統最后的噪聲沒什么影響。如果用一個2.61 K的電阻將AD8221的增益設定為20,也可以將所有的增益都放在前置放大級,而使AD8221的增益為1。而AD8599的增益帶寬積為10MHz。如果將總的增益都放在第一級,那么其帶寬將會被限制在20 kHz。在兩個元件之間分配增益,得到總帶寬大約為300 kHz。