在集成電路發(fā)展的數(shù)十年里,封裝形式從最典型的DIP、QFP發(fā)展到系統(tǒng)級SiP封裝和PoP封裝(Package on Package),再到如今的2.5D、3D高階封裝,封裝技術和集成度得到了顯著提升。

2.5D封裝簡介

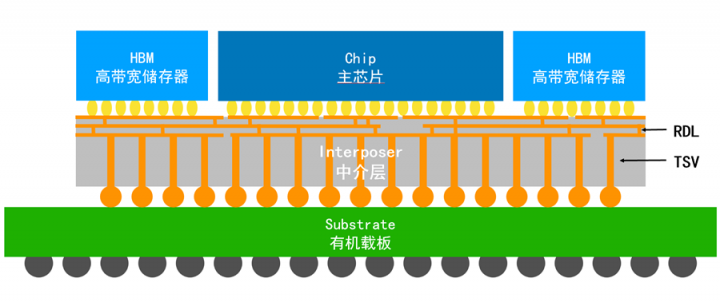

2.5D封裝通常應用于高性能的CPU、FPGA和人工智能等領域。它是一種將主邏輯芯片和HBM高帶寬儲存器等芯片同時集成的封裝形式,具體的封裝結構因廠家而異,主流的技術路線包括英特爾的EMIB和臺積電的CoWoS。以CoWoS為例,它是由Chip on Wafer on?Substrate縮寫而來,即先將各主芯片和儲存器集成堆疊到無源的Wafer(中介層)上,再將CoW部分封裝在有機載板Substrate上。

2.5D封裝芯片的典型結構

2.5D封裝芯片的典型結構

Interposer上的RDL使得各芯片之間的電信號可以直接交流,并通過Interposer中的硅通孔(TSV)傳輸?shù)接袡C載板以完成與外界的連接。這種封裝形式具有以下優(yōu)點:

1、減小器件所占用的面積,充分利用縱向空間,降低功耗;

2、縮短各芯片之間的電信號傳輸距離,減少導線寄生電容的影響。

然而,復雜的封裝過程也增加了制程工藝的難度,導致某些制程環(huán)節(jié)成本高昂以及整體良率下降等問題。

Cross Section切片剖面觀察

切片制樣是常見的破壞性物理分析手段,常見于檢查器件內(nèi)部結構或缺陷等場景。在制樣過程中,需要避免人為引入的noise和crack,否則將影響我們對器件本身的缺陷的判斷。

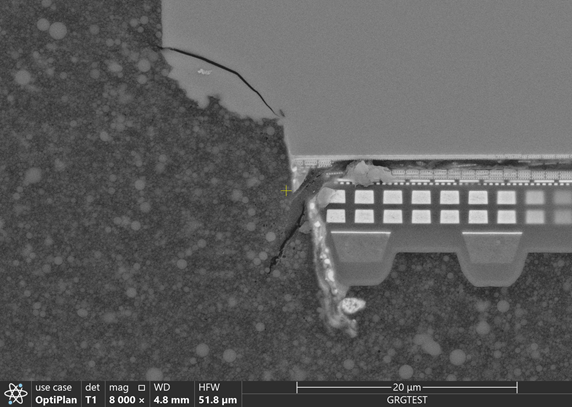

難點1:避免機械應力對芯片結構的異常損傷

在復雜封裝如2.5D,3D封裝中,主芯片為通常采用ELK材質(zhì)工藝的先進制程芯片,由于ELK材質(zhì)自身對機械應力承受能力較低的特點,在切片制樣過程中極易出現(xiàn)研磨導致金屬布線層出現(xiàn)Crack,嚴重的甚至會使金屬布線層與襯底直接分層。

圖2 2.5D封裝切片制樣裂紋的典型形貌

圖2 2.5D封裝切片制樣裂紋的典型形貌

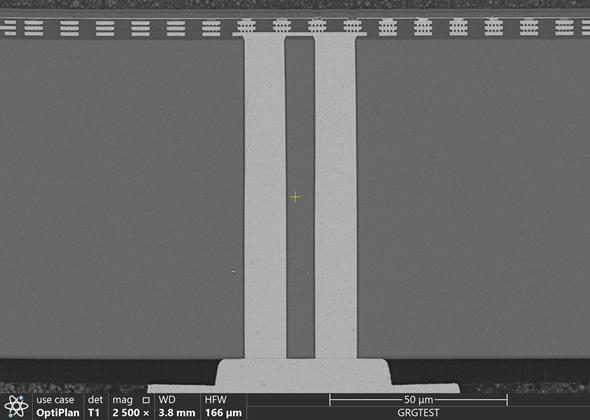

難點2:微結構尺寸較小易磨過位置

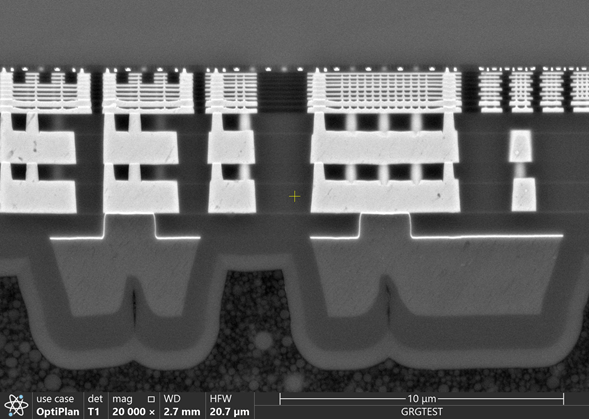

一般采用復雜封裝如2.5D封裝形式的器件,整體尺寸可超過5*5cm,但是,器件內(nèi)部的關鍵結構尺寸卻在微米級。如下圖,TSV孔在同一排中可存在超過150個相同的結構,每個TSV孔直徑僅10微米。要保證所有結構都能同時呈現(xiàn)在一個截面中,切片制樣時左右兩端研磨深度誤差就不能超過10微米;需要在研磨過程中進行精細控制。

圖3 TSV通孔剖面形貌

圖3 TSV通孔剖面形貌

廣電計量的服務優(yōu)勢

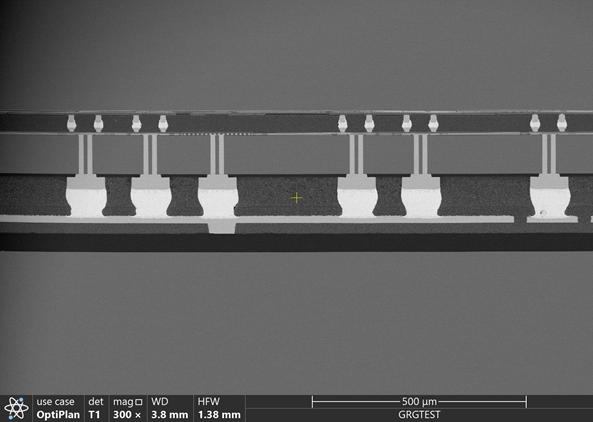

廣電計量DPA團隊,通過多年在高階封裝的DPA分析技術上的不斷探索,在高階封裝的DPA(破壞性物理分析)領域積累了大量的經(jīng)驗;能夠?qū)CBGA,COWOS,SIP,F(xiàn)OP等復雜封裝集成電路進行定點切片制樣的同時不會引入結構分層,開裂等制樣異常。同時配合OM,SEM等微觀分析技術,可以進一步分析高階封裝內(nèi)部的芯片互聯(lián)工藝質(zhì)量,underfill填充質(zhì)量,芯片金屬電路工藝質(zhì)量以及復雜封裝的封裝應力篩查,失效形貌觀察等圖:

圖4 2.5D封裝剖面局部形貌(COWOS)

圖4 2.5D封裝剖面局部形貌(COWOS)

圖5 2.5D封裝芯片ELK位置局部形貌

圖5 2.5D封裝芯片ELK位置局部形貌